# **SESSION**

# COMMUNICATION SYSTEMS: MOBILE COMPUTING, INTERCONNECTION NETWORKS AND TOPOLOGIES, WIRELESS SYSTEMS

Chair(s)

TBA

# **RM-circuits: Toward Feasible Use of Reconfigurable Mesh** Algorithms

Yosi Ben-Asher CS, University of Haifa Esti Stein CS, Tel Aviv-Yaffo Academic College Vladislav Tartakovsky CS, University of Haifa

Abstract—The reconfigurable mesh (RM) is a powerful model for parallel computations that can outperform PRAM computation. Many basic algorithms has been shown to run in constant time on the RM. In spite of this power, the RM has not been realized mainly due to the theoretical assumption of constant time broadcasting, while practically its a function of the number of switches the broadcast has to pass through. We introduce the restricted-RM (RRM) model, wherein buses use mostly  $d(n) = n^{1/k}$  switches. We show that counting the number of 1's in an n-bits input, can be done on the RRM in  $2 \cdot k$  steps for  $k = 2, 3, \dots$  An almost matching lower bound is presented, showing that the RRM cannot compute counting of n variables in less than k steps. Finally, the algorithm was directly coded in Verilog outperforming a regular optimal parallel adders-circuit. This work thus present a practical version of the RM which is directly coded as a hardwarecircuit showing not only that RM-algorithms are practical but also a simple way to program them.

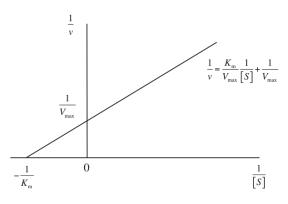

### 1. Introduction

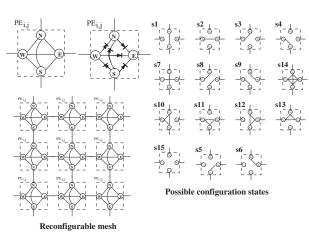

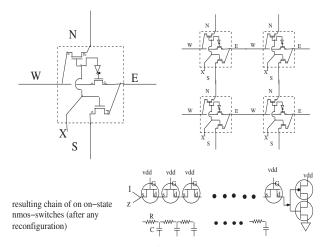

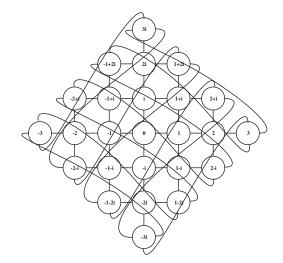

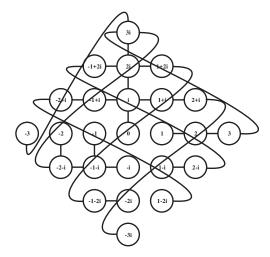

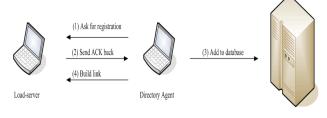

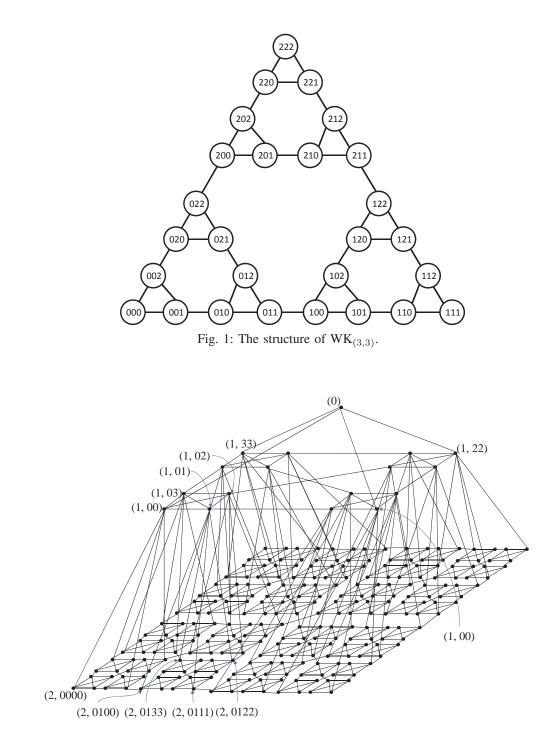

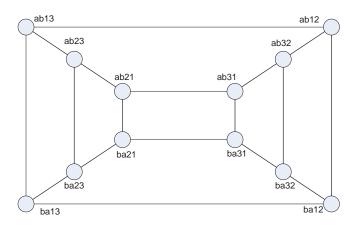

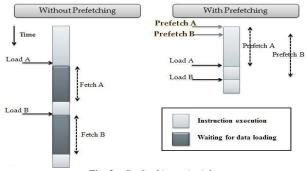

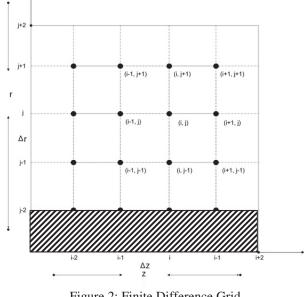

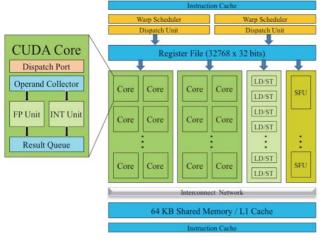

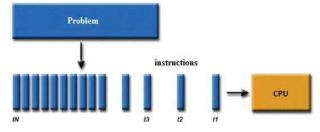

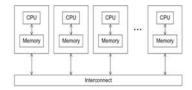

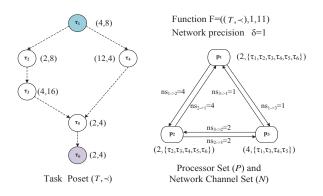

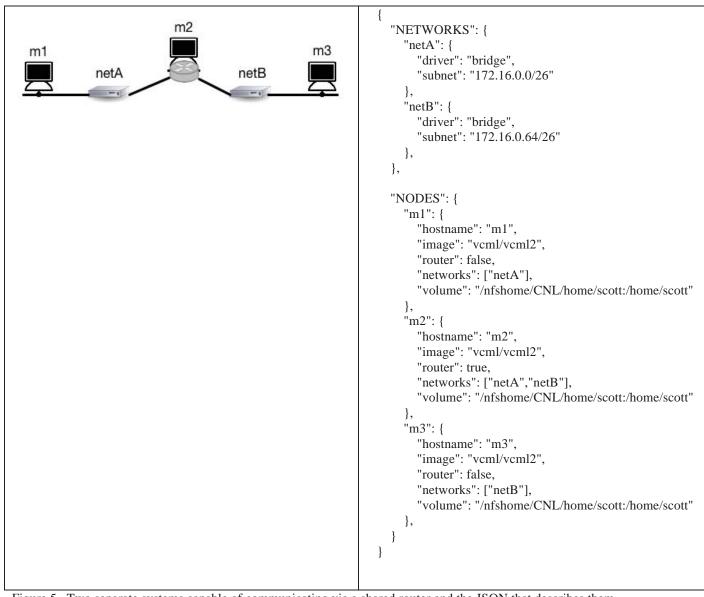

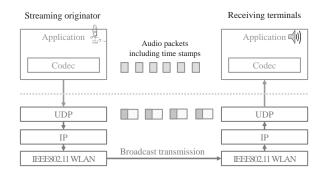

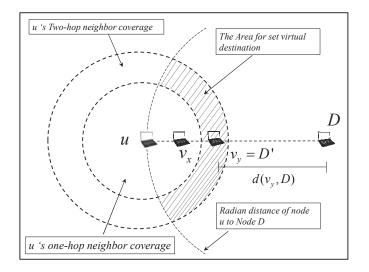

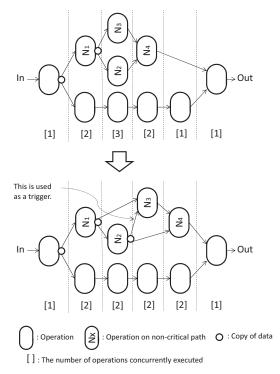

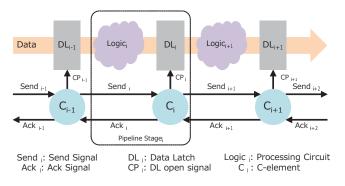

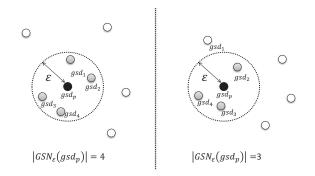

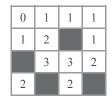

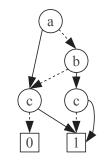

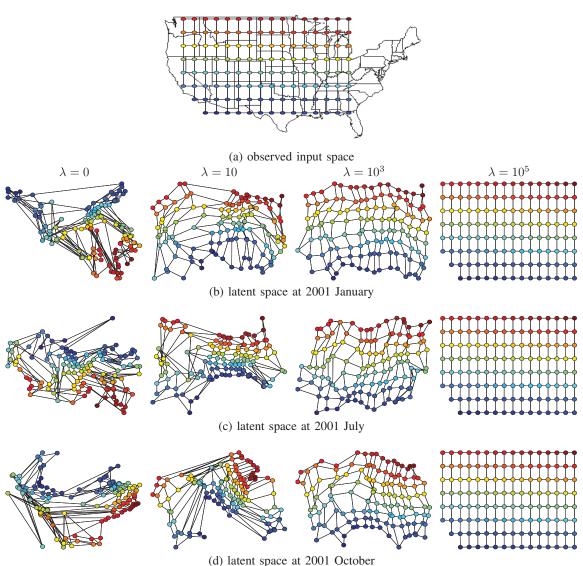

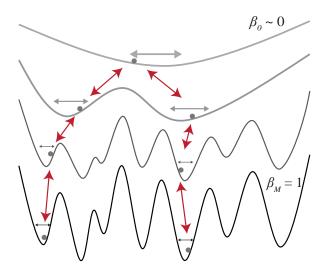

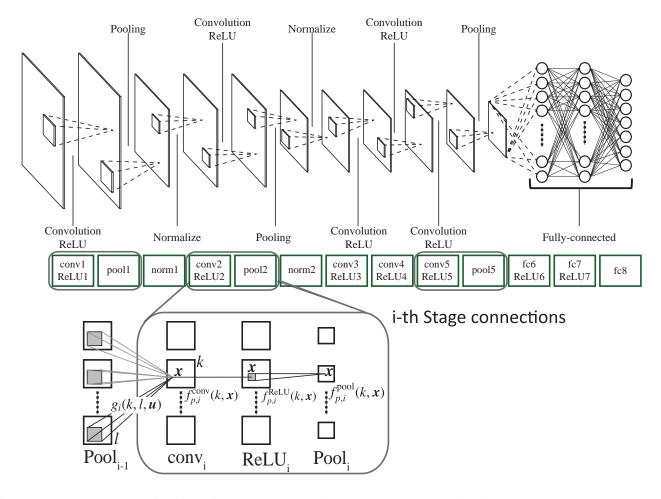

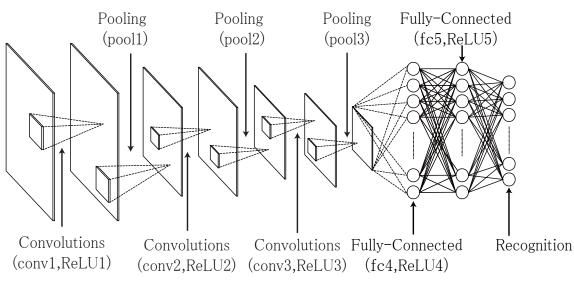

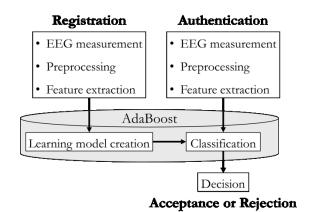

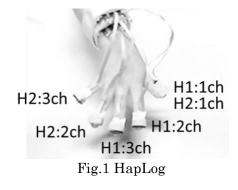

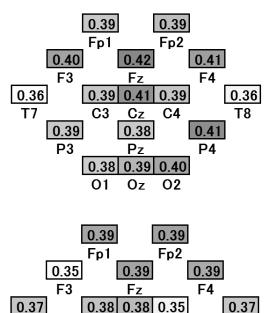

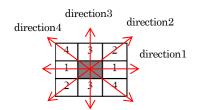

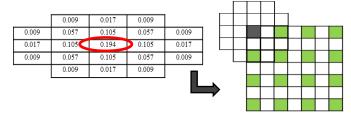

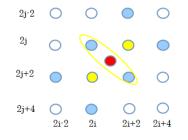

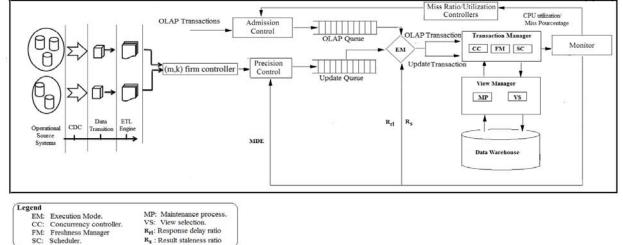

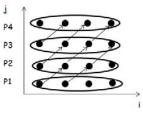

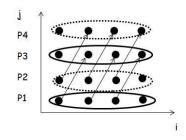

One of the most interesting models in the field of parallel computations is the reconfigurable mesh (RM). The RM consists of a mesh, augmented by the addition of a dynamic bus system, whose configuration changes in response to computation and communication needs. More precisely, a RM of size  $N \times N$  consists of  $N^2$  identical processing elements  $(PE_{i,j})$  as described in figure 1. Each  $PE_{i,j}$  is connected to its four neighbors  $PE_{i-1,j}$ ,  $PE_{i+1,j}$ ,  $PE_{i,j-1}$ and  $PE_{i,j+1}$  provided they exist, and has four ports denoted by 'N', 'S', 'E' and 'W'. Local connections within the PE can be dynamically changed at each step of the RM using on-off switches (figure 1 depicts 15 possible reconfiguration states). This yields a variety of possible bus topologies for the mesh, where each connected component is viewed as a single bus. In every broadcast step, each PE receives incoming signals, executes local computations, chooses a new configuration and broadcasts on some of its S, N, E, W edges (ports).

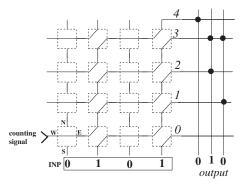

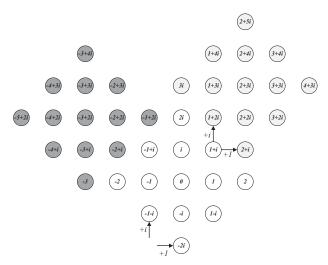

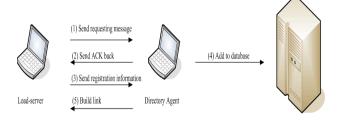

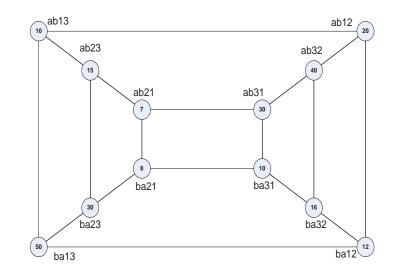

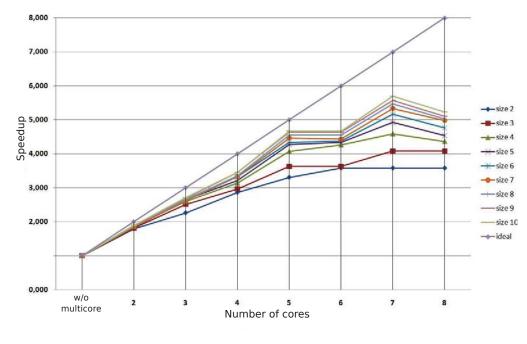

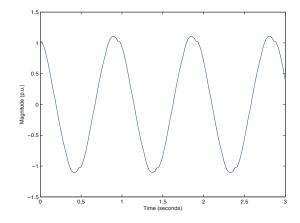

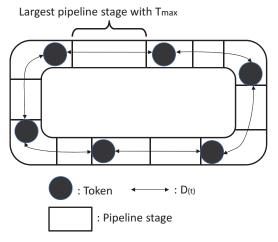

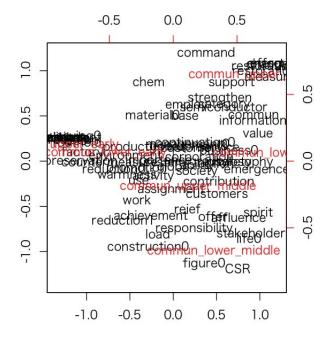

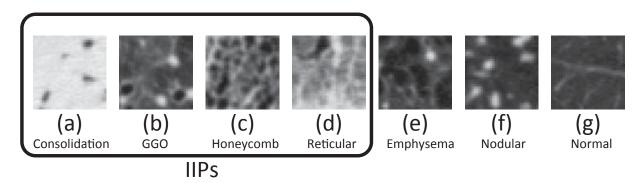

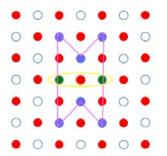

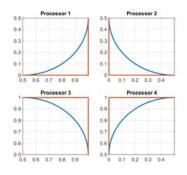

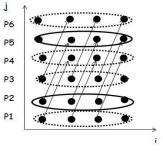

Counting the number of bits set to '1' in an input vector, is a fundamental operation of the RM. It is used in almost every RM algorithm, and is performed in many variations. Consequently, when introducing a new RM model, it is important to study its complexity in this model. Figure 2 depicts how counting is applied to a 4-bits input using a  $4 \times 4$  RM. Based

Fig. 1: Reconfigurable mesh and all 15 possible states

on the *i*'th input bit, each switch in column-*i* of the RM choose either to perform a "band"  $\langle W \Longrightarrow N, S \Longrightarrow E \rangle$ or a "horizontal-pass"  $\langle W \Longrightarrow E, S, N \rangle$ . As a result, an incoming signal (> in figure 2, bottom-left) is banded where INP[i] == 1, and the output signal comes out through the k'th output iff  $\sum_{i=0}^{N} INP[i] = k$ . Note that since we are targeting a circuit, we can freely use wires connecting different RM switches, and also input bits. Thus, as shown in figure 2, the task of converting the position (0, 1, 2, 3, 4) of the output signal to a binary number is done via connecting each possible position to its binary representation using  $\log 4 + 1$  vertical wires. Counting of N input bits takes one step on  $N \times N$  RM, using broadcasts that traverse N switches. It is thus not immediate to find a counting algorithm for the restricted RM using buses of length less than or equal to d(N), maintaining minimal possible number of steps. Moreover, a lower bound for counting on the restricted RM should be devised, so that optimal values of d(N) can be determined.

As such it has been shown that the RM can perform parallel computations faster than boolean circuits or by the PRAM (Parallel Random Access Machine) model [15]. This include O(1) summing [14], [5], O(1) multiplication [12], sorting [13], convex hall [19], graph algorithms [6], [23] and image processing [16]. However, this potential power of the RM could not practically be used, since the RM model assumes that broadcasting a signal along a bus/connected

Fig. 2: Counting on the reconfigurable mesh

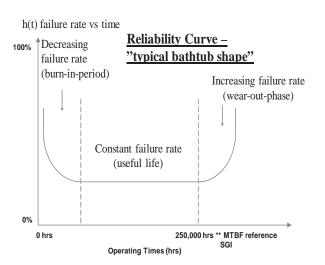

component can be done in one step regardless of the number of switches/ports it passes. This assumption is not feasible using current CMOS transistors since the dynamic reconfigurations inside each PE must be realized by switches connecting/disconnecting its S, N, E, W edges. As switches are made from CMOS transistors, each with a *Resistance* · *Capacity* delay for ON/connected-state, broadcasting along a bus composed of n switches, is at least  $n \cdot R \cdot C$  which is in contrast to the O(1) assumption. In fact, using the Elmore model [9] to estimate the delay along n switches, yields a quadratic delay of  $(n^2)/2 \cdot R \cdot C$ . This is due the time required to fill  $C_i$  (the capacitance of the *i*'th switch of the bus), which is proportional to  $(i \cdot R)$ .

Several types of restricted models such as the RMBM (Reconfigurable Multiple Bus Machine) [22] have been proposed. Since all of them are using n switches on an n length bus, they are not good candidates to solve the above problem. One restricted model that is closer to the proposed restricted RM is the SRGA of [21], [8], where each row/column of the mesh has a complete binary tree of reconfigurable switches, allowing to route messages between the leaves of this tree. However, the SRGA still allow broadcasts that pass through O(N) switches. A more related work is [4] proposing kconstrained RM model that allows buses of wire-size at most k to be formed per cycle. [4] shows that a version of columnsort [18] can sort N items on the k-constrained  $k \times N$  RM in O(N/k) steps (and a similar result for convex hull). This implies that sorting on the k-constrained RM has optimal VLSI complexity of  $A \cdot T^2$ , mainly due to the linear O(N)bus configurations of the sorting algorithm, which can be optimally simulated in N/k steps by the k-constrained RM. We remark that optimal self simulations for the RM with linear bus configurations has been shown in [2], hence any RM algorithm that uses only linear buses can be efficiently simulated by k-constrained RM. This work differs from [4] as we go beyond simulation of larger buses over small buses and ask a different question: what is the minimum number of switches (length) on a bus, forming a restricted RM, that can be a platform for solving a problem running on a non-restricted RM, without increasing time complexity. For example, in order to execute counting of N bits by an  $N \times N$  RM in a constant number of steps, one should use buses of length  $N^{\frac{1}{k}}$ . In comparison, had we just simulated the N-bus of the regular  $N \times N$  counting by buses of length  $N^{\frac{1}{k}}$  we would have end with  $N^{\frac{k-1}{k}}$  steps using [4], rather than the k steps we obtain. In addition, our model focuses on the number of switches a broadcast goes through compared to the length of bus, since the main delay on the RM bus is quadratic in the number of switches.

Thus in this work we study a new model of the RM called the "restricted-RM" (RRM) wherein broadcasting along buses is restricted not to use or pass through more than d(n) switches where n is the input size. For example if  $d(n) = n^{\frac{1}{4}}$  then for  $n = 10^6$  we get that  $d(n) \approx 30$ , a number for which the RM O(1) assumption may be feasible, using current transistors technology. Thus, we believe that by restricting broadcast to pass through no more than d(n) switches we can obtain RM circuits that are feasible and outperform their regular gate-based circuits. We study the fundamental problem of counting the number of 1 bits in an input sequence of n variables and show that:

- Counting can be done using the RRM with d(n) = n<sup>1/k</sup>

in 2k steps for any constant value of k = 2, 3, ....

- An almost matching lower bound showing that a RRM with  $d(n) = n^{1/k}$  can not compute counting of n variables in less than k + 1 steps. Proving lower bounds for reconfigurable algorithm is more difficult than regular lower-bounds, due to the need to bound information that can be obtained by reconfiguration. The technique presented in this work adds to the few existing lower-bound techniques proposed so far (e.g. [1]).

- We show that RM-algorithm can be directly coded in Verilog. This way of programming RM-algorithms overcome most of the drawbacks of the C-like programing style proposed so far for RM-algorithms (e.g.,ARMlang [10]). We thus demonstrate that RM algorithms can be directly synthesized to circuits using hardware description language even for large size of RMs. Previous realizations of the RM were mainly to a small-size grid of Soft-CPUs on the FPGA using MUX-gates for reconfiguration. Clearly this method [11] can not scale well.

## 2. Counting with the Restricted RM

We first indicate that the restricted RM (RRM) model we consider is a form of a circuit. Therefore, wires and logic/arithmetic sub-circuits can be used freely. We can thus use a set of x subRMs each of size  $z \cdot w$  where fix wires can arbitrarily connect between the processing units of these subRMs. We refer to such a circuit of subRMs as a RRM of size  $z \times x \cdot w$ .

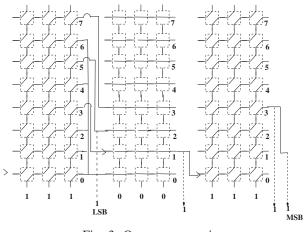

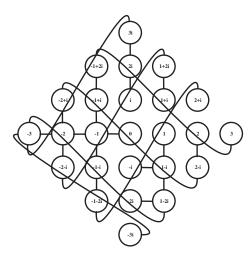

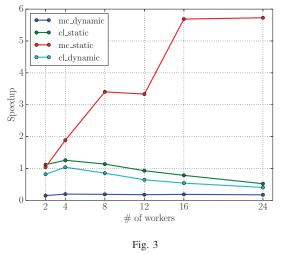

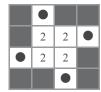

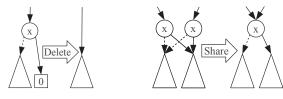

The ability to perform counting on a RRM requires an ability to sum numbers. Therefore, we use a simple RM

Fig. 3: One step summing

technique for summing:

Theorem 2.1: Summing of L binary numbers  $x_1, \ldots, x_L$  of L input bits each, can be done in one step by a  $2 \cdot L \times L^2$  RRM using bus lengths of at most  $L^2$  switches.

This can be done by concatenating L RMs, each of size  $2 \cdot L \times L$   $(RM_1, \ldots, RM_L)$  such that each  $RM_i$  computes counting of the *i*'th bits of each number,  $y_i = counting_{input\_signal, RM_i}(x_1[i], \ldots, x_L[i])$ . The position of the output signal of  $RM_i$  is converted to an output bit  $y_i = i \mod 2$  such that  $y_L, \ldots, y_1$  form the final sum. The input\\_signal of  $RM_{i+1}$  is either:

- fed to RM<sub>i+1</sub>[0][0] if the output position of RM<sub>i</sub> is zero or

- fed to RM<sub>i+1</sub>[0][k] if the output position of RM<sub>i</sub> is 2⋅k (by "banding" the output bus).

The validity of this construction follows from the fact that each 1-value at column-*i* represents  $2^i$  in the final sum, thus the carry from column i - 1 should be the number of 1s divided by 2. Figure 3 depicts the summing for the case of L = 3 where 101 + 101 + 101 = 1111. This simple construction (plus some other known techniques [3], [17], [12]) yields that multiplications, parallel sums, divisions and shift operations can be performed in one parallel step using RMs.

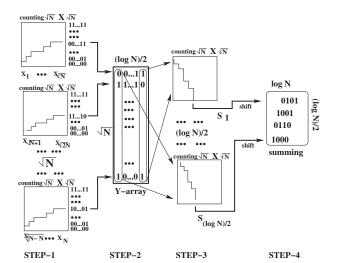

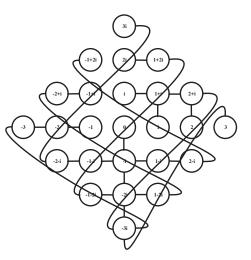

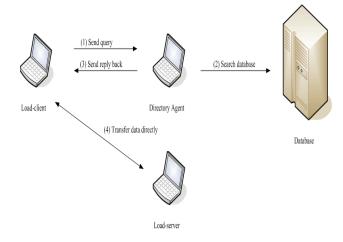

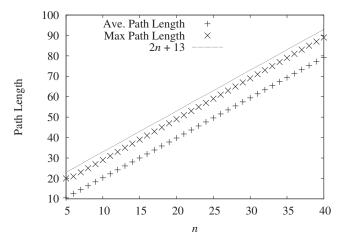

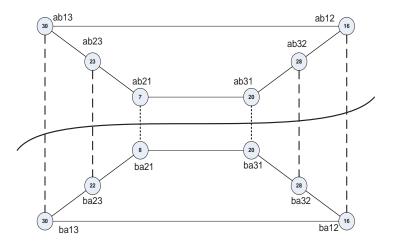

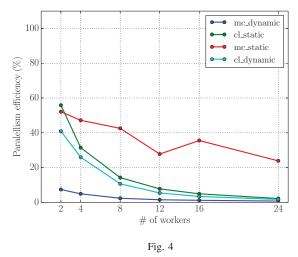

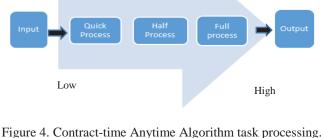

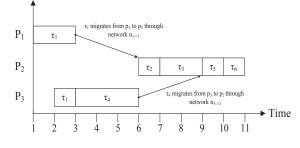

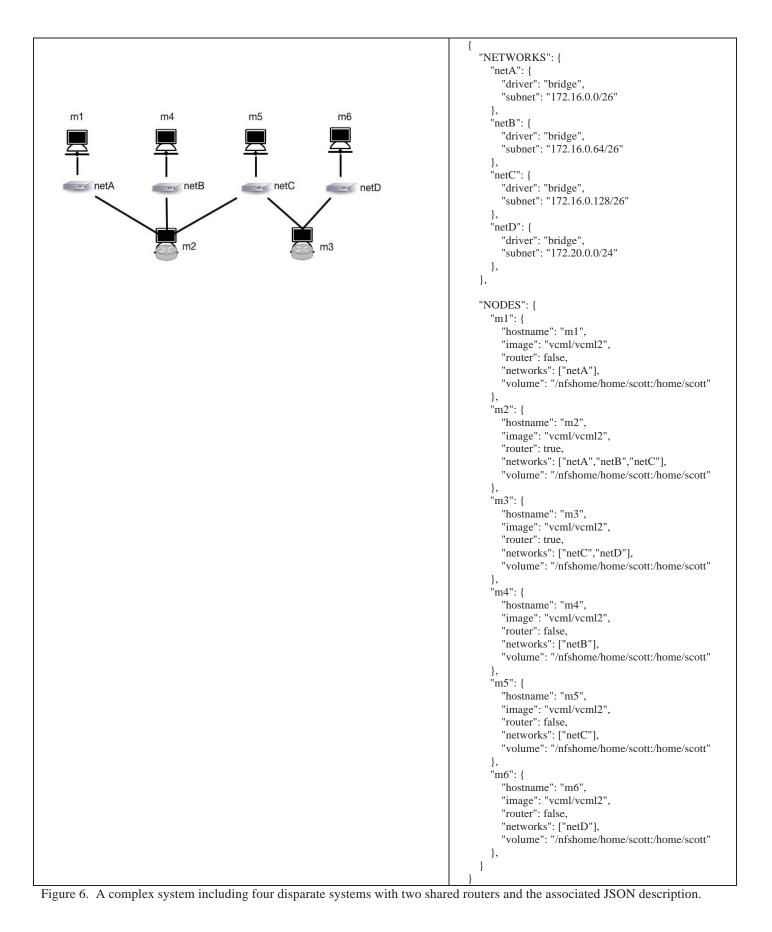

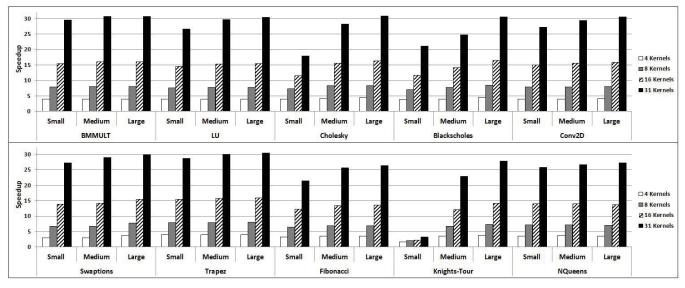

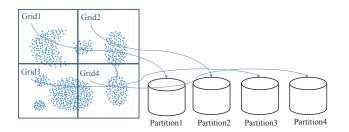

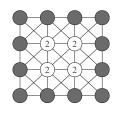

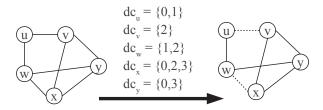

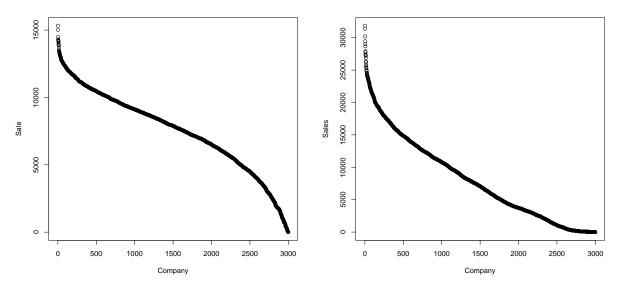

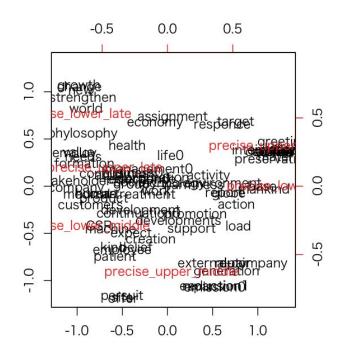

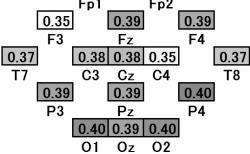

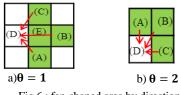

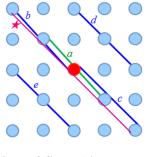

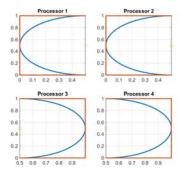

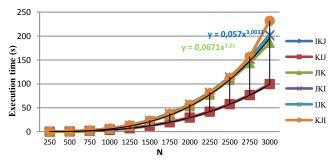

Next, we consider counting where the RM is restricted to use buses of length  $\leq N^{\frac{1}{2}}$  where N is the input size. The algorithm is depicted in figure 4 and contains the following four steps:

$restricted\_counting_2(N, x_1, \ldots, x_N)$ :

- STEP-1 A set  $RM_1, \ldots, RM_{N^{\frac{1}{2}}}$  each of size  $N^{\frac{1}{2}} \times N^{\frac{1}{2}}$ , computes counting of  $N^{\frac{1}{2}}$  input bits each. This yields  $N^{\frac{1}{2}}$  partial sums of  $(\log N)/2$  bits.

- STEP-2 The  $N^{\frac{1}{2}}$  partial sums are packed into  $N^{\frac{1}{2}} \times (\log N)/2$  array (denoted as Y-array in figure 4). This is done by broadcasting along  $(\log N)/2$  wires for each  $RM_i$ .

Fig. 4: Restricted counting for k = 2, schematic layout of the algorithm/circuit

- STEP-3 Counting of the  $N^{\frac{1}{2}}$  bits in each column of the Yarray is applied using  $RM_1, \ldots, RM_{(\log N)/2}$ . This yields  $(\log N)/2$  partial sums  $S_1, \ldots, S_{(\log N)/2}$  of  $(\log N)/2$  bits each.

- STEP-4 Summing of  $S_1, \ldots, S_{(\log N)/2}$  is performed using the RM described in theorem 2.1. Each  $S_i$  must be first shifted *i* positions since each 1 in column *i* of the Y array is  $2^i$ . Due to this shifting, we sum  $\frac{1}{2} \log N$  numbers of  $\log N$  bits. Thus we need a RM of  $\log N \times \frac{1}{2} \log^2 N$  RM to be used as described in theorem 2.1. Since all reconfiguration paths must be less than  $N^{\frac{1}{2}}$  we get that  $N^{\frac{1}{2}} > \frac{1}{2} \log^2 N$ .

Thus the following claim hold:

Theorem 2.2: For  $\frac{1}{2} \cdot (logN)^2 \leq N^{\frac{1}{2}}$ , counting of N input bits can be done in four steps by a  $N^{\frac{1}{2}} \times N$  RM restricted to  $N^{\frac{1}{2}}$  bus lengths.

This counting can be extended to  $d(N) = N^{1/k}$  k = 2, 3, 4, ... as follows. For the case k = 3 we can use the following steps:

$restricted\_counting_3(N, x_1, \ldots, x_N):$

- STEP-1 A set  $RM_1, \ldots, RM_{N^{\frac{2}{3}}}$  each of size  $N^{\frac{1}{3}} \times N^{\frac{1}{3}}$ RMs computes counting of  $N^{\frac{1}{3}}$  input bits each. This yields  $N^{\frac{2}{3}}$  partial sums of  $(\log N)/3$  bits.

- STEP-2 The  $N^{\frac{2}{3}}$  partial sums are packed into  $N^{\frac{2}{3}} \times (\log N)/3$  Y-array ( similar to the way it was done in figure 4).

STEP-3 Counting of the  $N^{\frac{2}{3}}$  bits in each column of this

Y-array is performed using

$$S_{(\log N)/3} = restricted\_counting_2(N^{\frac{2}{3}}, Y[(\log N)/3][1], \dots, Y[(\log N)/3][N^{\frac{2}{3}}])$$

Each  $S_i$  should be shifted according to its column position, i.e., *i* positions.

STEP-4 Summing of the shifted  $S_1, \ldots, S_{(\log N)/3}$  is performed using the algorithm of theorem 2.1. Hence, for the summing we need a RM of  $\frac{1}{3}\log N \times \frac{1}{3}\log^2 N$ . Consequently it follows that  $\frac{1}{3}\log^2 \leq N^{\frac{1}{3}}$ .

Clearly this recursive scheme can be used for any  $d(N) = N^{1/k}$   $k = 2, 3, 4, \dots$  using

$$S_i = restricted\_counting_{k-1}(N^{\frac{k-1}{k}}, Y[i][1], \dots, Y[i][N^{\frac{k-1}{k}}])$$

The following claim holds:

Theorem 2.3: For  $\frac{1}{k}\log^2 N \leq N^{\frac{1}{k}}$ , counting of N input bits can be done in  $2 \cdot k$  steps by a RM restricted to  $N^{\frac{1}{k}}$  bus lengths.

Finally, we can solve the condition  $\frac{1}{k}\log^2 N \leq N^{\frac{1}{k}}$  as follows:

• Using the fact that  $N^{\frac{\log \log N}{\log N}} = \log N$  we get that

$$\log^2 N \leq N^{\frac{1}{k}} \iff k \leq \frac{\log N}{2 \cdot \log \log N} \quad (1)$$

• Applying some calculations (omitted due to space limitations) to this equation we can improve this bound to:

$$\log^2 N \leq N^{\frac{1}{k}} \iff k \leq \frac{\log N}{\log \log N + 2 \cdot \log \log \log N}$$

(2)

For example, if  $N = 2^{32}$  then the first bound implies  $k = \frac{32}{2 \cdot 5} = 3.3$  while the second bound yields that k = 4 which is the correct result.

We remark that by adding another step (STEP-3.5) to the *restricted\_counting*<sub>2</sub> algorithm, repeating the partial sums calculations, we can end with  $(\log N)/2$  partial sums each of a size of  $(\log \log N)$ . By carefully wire the results, we can end using a smaller RM for the final summing of a length of  $\frac{1}{2} \log N \cdot \log \log N$ . This gives us a higher k for the same N, since  $\frac{1}{k} \log N \cdot \log \log N \leq N^{\frac{1}{k}}$  holds.

## 3. Lower bound

An almost matching lower bound for counting can be shown for the RRM. However, due to space limitation its proof has been omitted. The lower bound works by replacing a T-steps computation of the RM by a stronger model of Tnon-deterministic levels of Branching programs  $B^1, \ldots B^T$ such that:

B<sup>1</sup> is any polynomial (in N) DAG whose some of its edges are labeled by input variables x<sub>i</sub>, ¬x<sub>i</sub>. Based on the input values edges whose label are false, are disconnected.

B<sup>t>1</sup> is any polynomial (in N) DAG whose some of its edges are labeled by e<sub>i</sub>, ¬e<sub>i</sub> where e<sub>i</sub> are edges of B<sup>t-1</sup>. An edge labeled e<sub>i</sub> in B<sup>t-1</sup> is valued true iff there is a path from a leaf node in B<sup>t-1</sup> to e<sub>i</sub> (vice versa for edges labeled ¬e<sup>i</sup>).

We show that

*Lemma 3.1:* A d-restricted (#labeled edges in any path)  $LBP^T$ ,  $d = N^{\frac{1}{k}}/k$ , cannot compute the function  $f(x_1, x_2, \ldots, x_n) = \sum x_i = n/2$  (and hence counting) in less than k + 1 steps.

In addition we show that  $LBP^T$  can simulate any T steps of the RM. Consequently, we get matching lower bound for counting showing the optimality of the above algorithm.

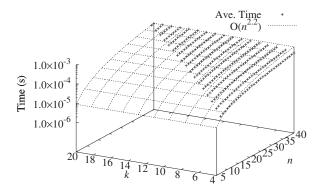

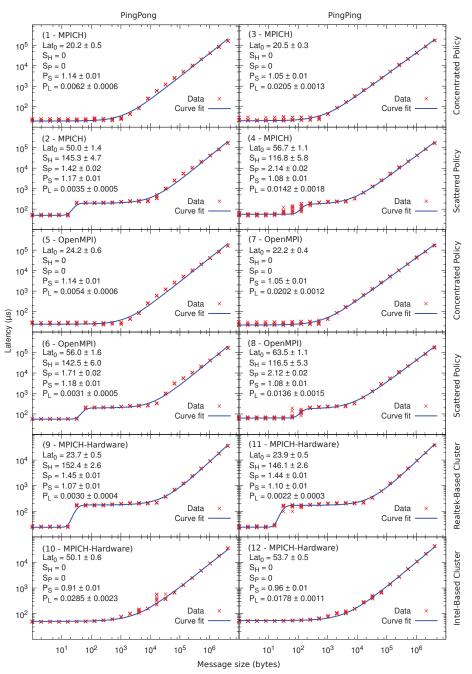

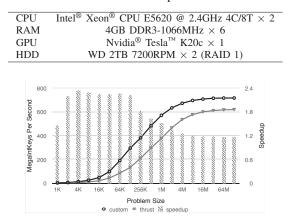

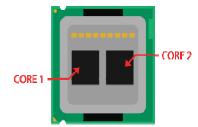

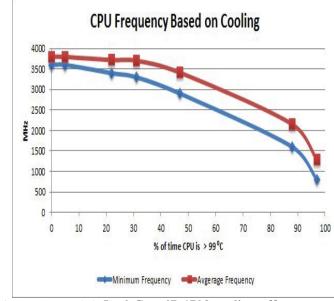

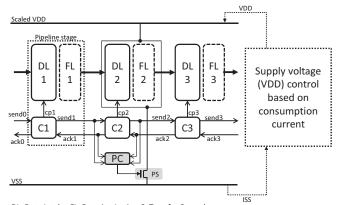

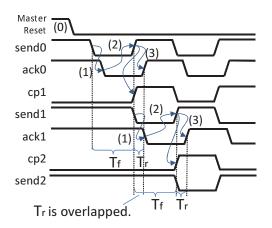

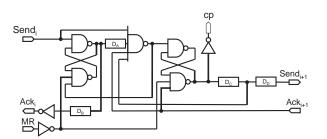

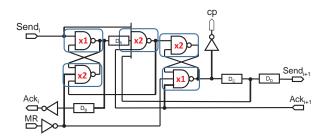

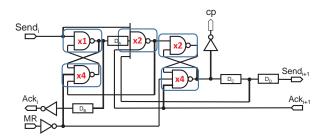

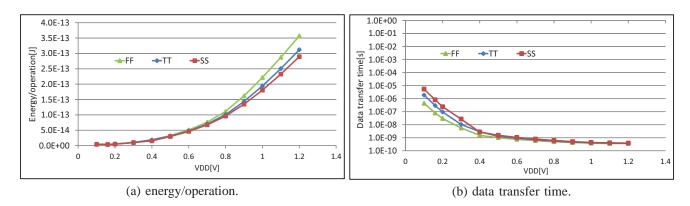

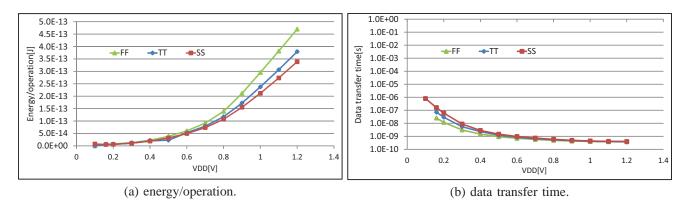

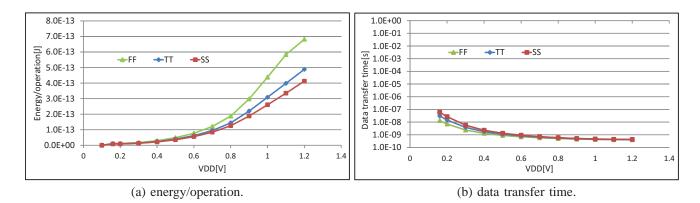

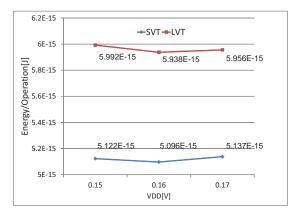

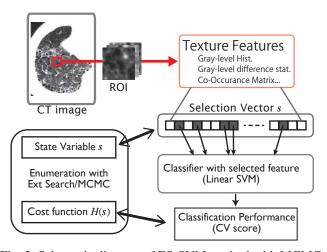

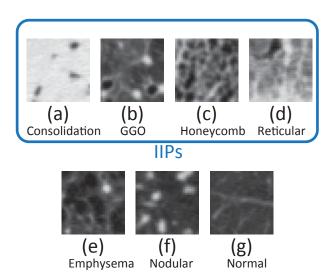

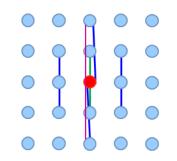

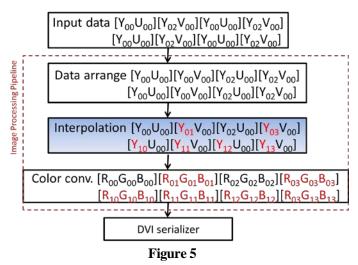

## 4. Feasibility and FPGA results

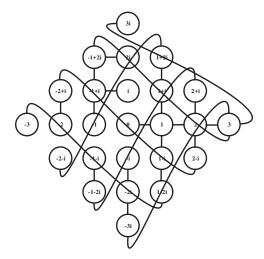

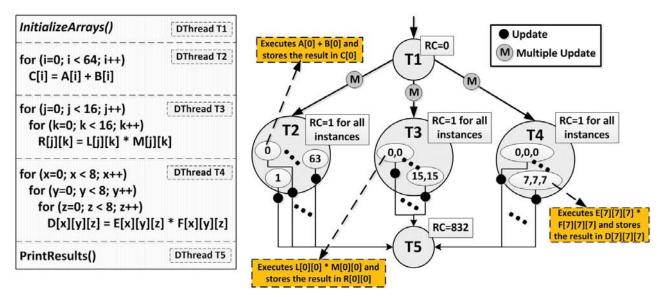

Two realizations of the RM switch for the RM-counting are presented, followed by comparisons between the delay for a  $d(n) \times d(n)$  RM-counting in our algorithm, and equivalent realizations of an adder based circuit. Finally, we show a comparison of the two mentioned methods synthesized on an FPGA using Xilinx Vivado. The RM switch for the RMcounting is realized using three basic on-off switches as described in figure 1 (upper left part). There are two possible states  $\langle W \longrightarrow N, S \longrightarrow E \rangle$  and  $\langle W \longrightarrow E, S, N \rangle$ that are determined by a control bit x directly connected to an input bit. The state of each basic switch can be either connect or disconnect generating the required configuration. Figure 5 describes the realization of the RM-switch using three NMS transistors to implement the basic on-off switches we need. These three transistors are controlled by the input value Xand one inverter. The following holds:

- Only the nmos transistors along the signal-path are in on-state, the rest are in-off state and all basically disconnected from the transistors of the signal path.

- The voltage after each transistor along such a chain of nmos-transistors is  $vdd v_{threshold}$ , thus there is no need to insert buffers to restore the signal strength.

- An nmos-transistor at on-state can be regarded as a source-drain resistor of resistance R + capacitor with capacitance C to the ground. Thus, the delay along a chain of  $N^{\frac{1}{k}}$  nmos transistors, is based on Elmore model,  $N^{\frac{2}{k}} \cdot \frac{R \cdot C}{2}$ . The capacitors of the rest of the transistors and the inverter can be ignored while computing the delay of  $N^{\frac{1}{k}} \times N^{\frac{1}{k}}$  counting RM.

The implementation for RRM counting of N inputs and k levels contains:

k levels of N<sup>1/k</sup> × N<sup>1/k</sup> sub-RMs to perform the different counting operations of STEP-1 (see figure 4). Once all switches have been configured, the counting signal (see figure 2) needs to traverse N<sup>1/k</sup> switches to the output of this step. This is referred as the signal critical path.

Fig. 5: NMOS realization of the RM switch and equivalent RC chain of the signal path

2) k levels of summing where each summing is applied to at most  $\frac{\log N}{k}$  numbers in  $\frac{k+1}{k}$  bits of STEP-4 (see figure 4). The resulting sum-RM needed for this summing is of size  $\frac{\log N}{k} \times \frac{\log N}{k} \cdot \log N$ , which is still in the restriction of  $d(n) \leq N^{\frac{1}{k}}$ . This is because we have selected the suitable value for k from eq. 1,2.

Thus, all signal paths are of the same length and the delay for restricted counting is  $2k \cdot N^{\frac{2}{k}} \cdot \frac{R \cdot C}{2}$

This delay should be compared to the delay of a CMOS circuit that computes counting of N inputs using a complete binary tree of adders:

- $\log N$  adders in each path of this summing tree.

- Each adder has depth (critical path) of 4 + 2 ⋅ log log N gates (see [20]).

- Each gate has a critical path of two-three CMOS transistors.

- The switching delay of each CMOS transistor can be estimated by  $2 \cdot R \cdot C$ , counting for the delay to switch each transistor to conducting state + source-drain propagation delay of the current.

$tree_of_adders_delay = \log N \cdot (4 + 2 \cdot \log \log N) \cdot 3 \cdot 2 \cdot R \cdot C$

For a given N, the restricted RM-counting will outperform the tree of adders circuit if

$\log N \cdot (4 + 2 \cdot \log \log N) \cdot 3 \cdot 2 \cdot R \cdot C \ge 2k \cdot N^{\frac{2}{k}} \cdot \frac{R \cdot C}{2}$

We get that

$$24 \cdot \log N + 12 \cdot \log N \cdot \log \log N \ge k \cdot N^{\frac{2}{k}}$$

This hold for most cases of  $N \ge 2^{16}$  and  $k \ge 4$ .

Another possibility to implement the RRM is to use Optical Ring Resonator (ORR) [7] which consists of silicon micro-ring resonator coupled to two straight wave-guide. Basically, ORR allows light to "jump" from one wave-guide ('L') to the other wave-guide 'R', when an electrical field is applied. Unlike CMOS transistors, this is done without any latency apart from the speed of light inside |L| + |R|. Note that ORR are directional and thus (ideally) light beams cannot propagate "backwards" in the switching network that we are building. The RM-switch work with one ORR and one Y-junction. Therefore, light coming from 'W' will continue either to 'N' or to 'E', depending on 'X'. However, light coming from 'S' will always continue to 'E'. For this optical realization, the delay calculation should be:

$\log N \cdot (4 + 2 \cdot \log \log N) \cdot 3 \cdot 2 \cdot R \cdot C \ge 2k \cdot N^{\frac{1}{k}} \cdot ORR\_dellay$

For current CMOS technology  $R \cdot C = 5ps$ , and

$ORR\_delay = ORR\_length/speed\_of\_light\_silicon = 82 \cdot 10^{-6} \cdot 208 \cdot 10^{6} = 0.4ps$

which is significantly faster for any value of N and k.

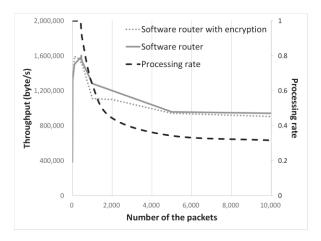

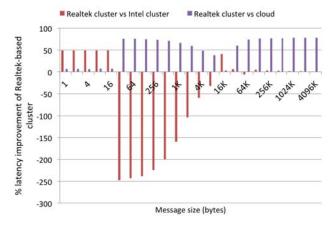

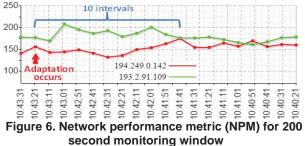

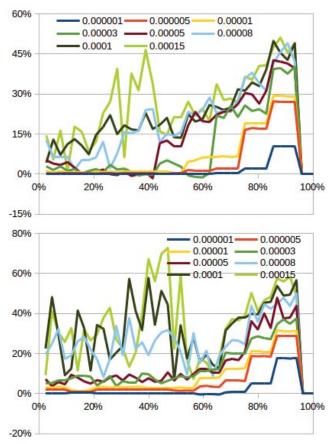

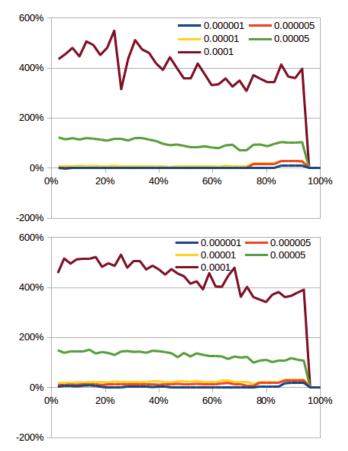

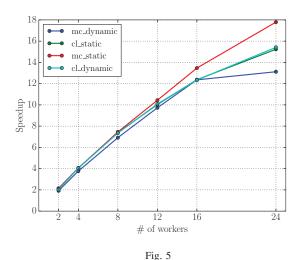

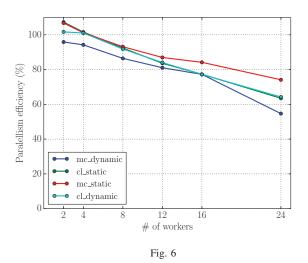

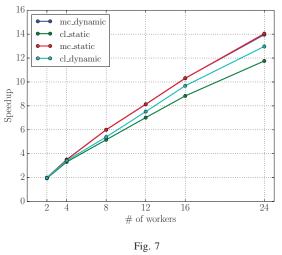

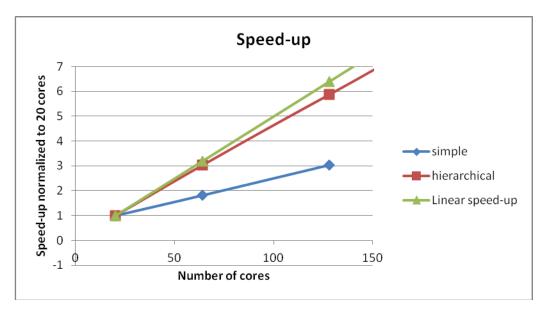

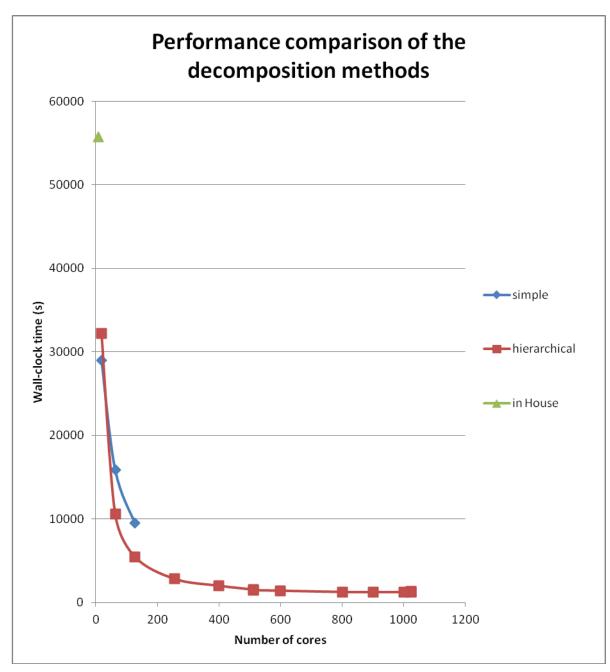

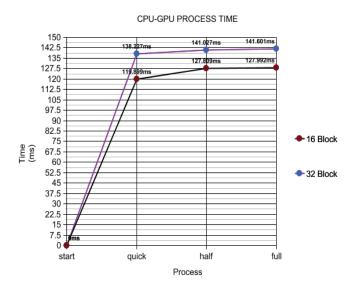

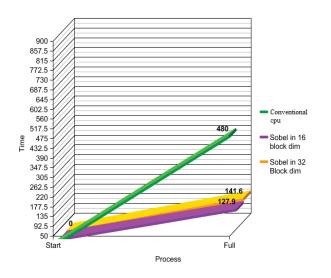

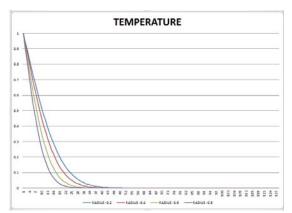

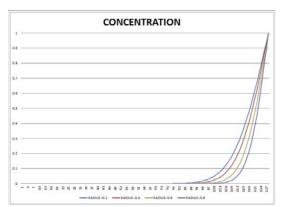

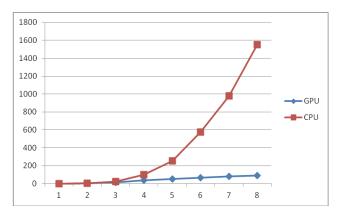

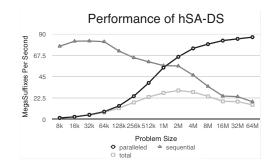

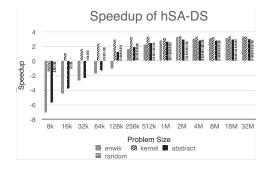

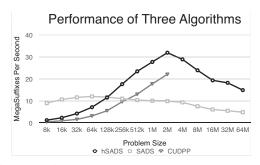

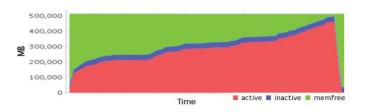

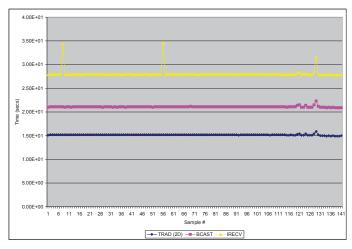

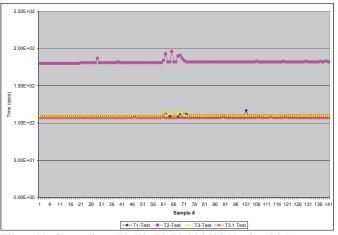

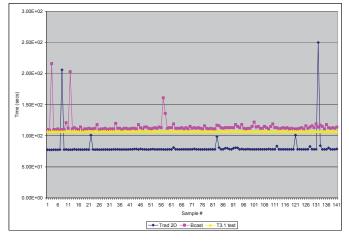

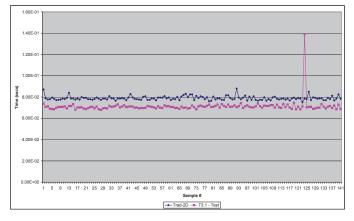

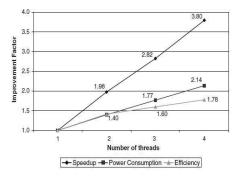

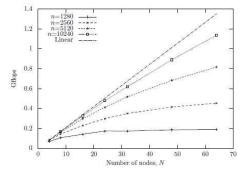

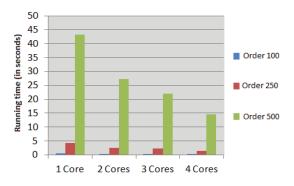

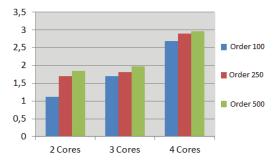

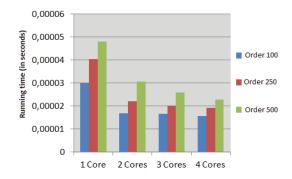

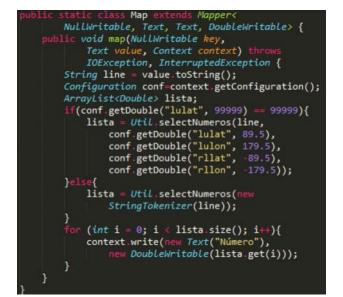

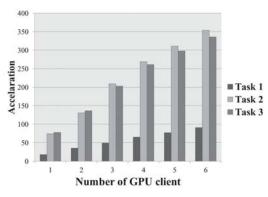

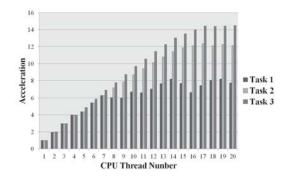

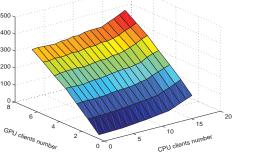

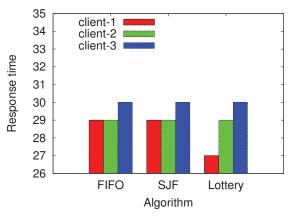

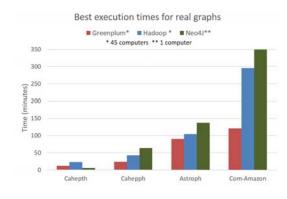

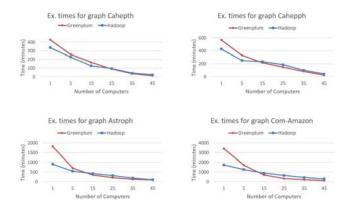

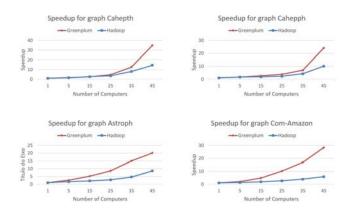

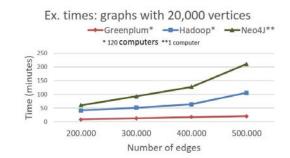

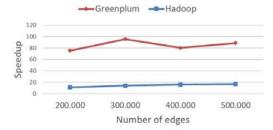

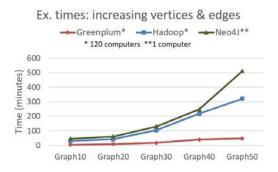

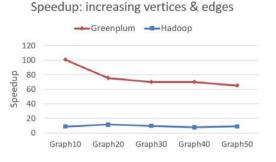

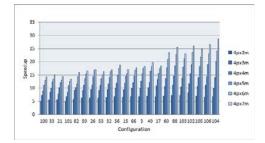

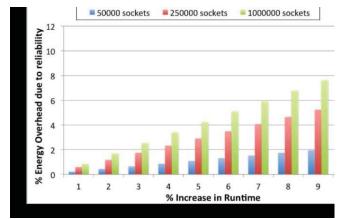

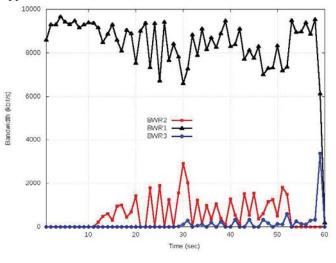

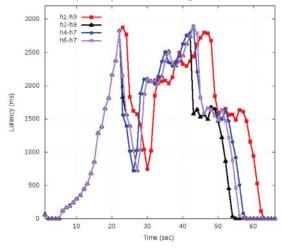

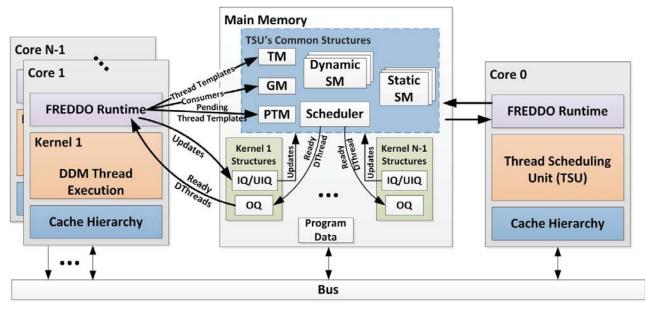

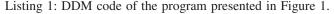

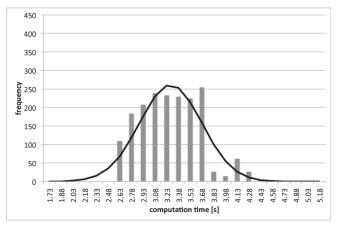

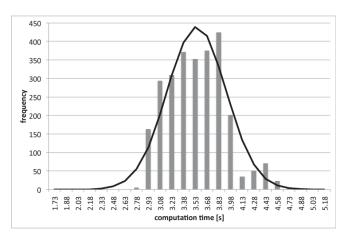

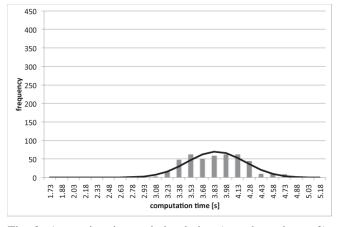

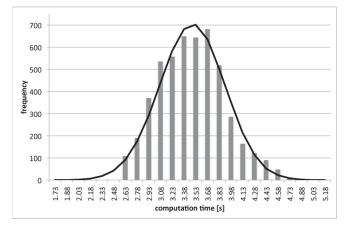

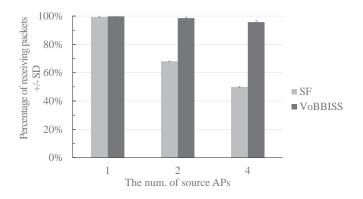

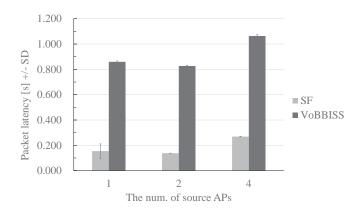

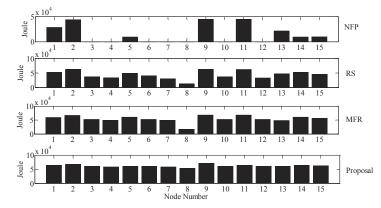

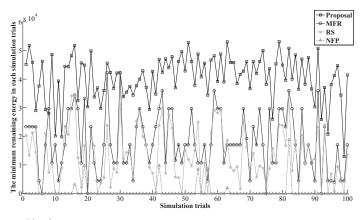

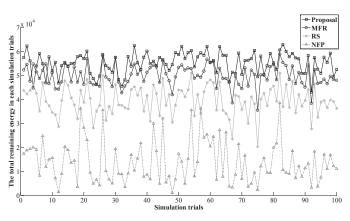

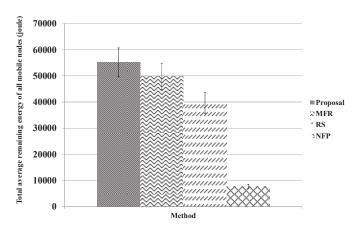

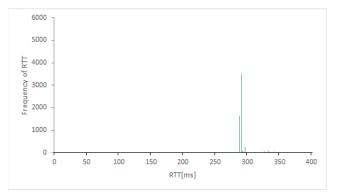

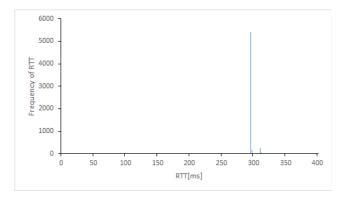

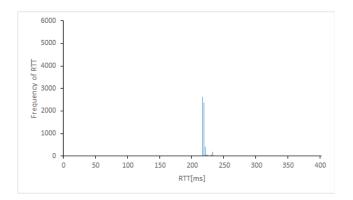

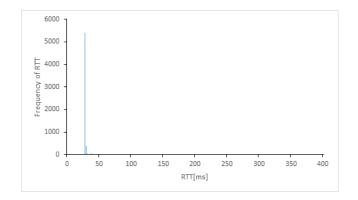

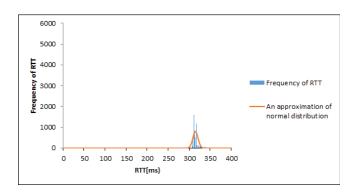

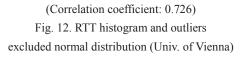

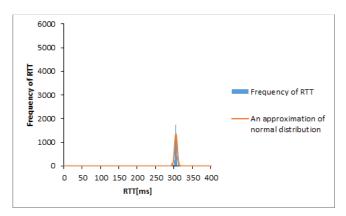

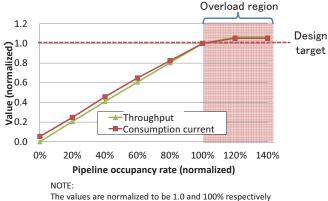

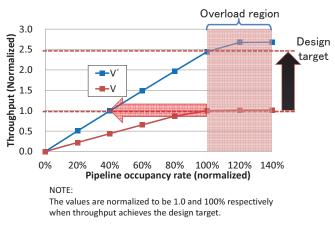

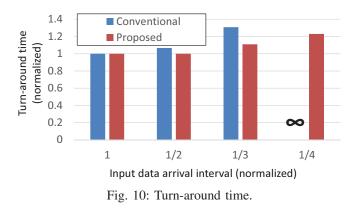

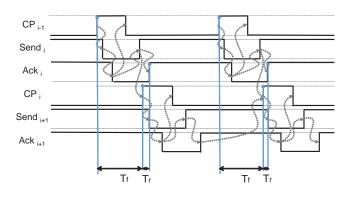

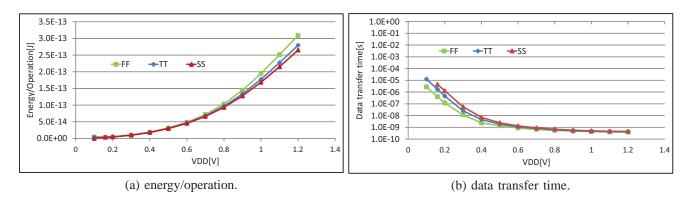

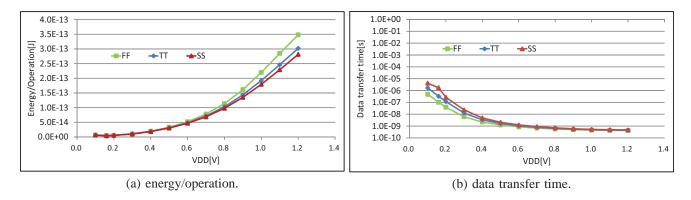

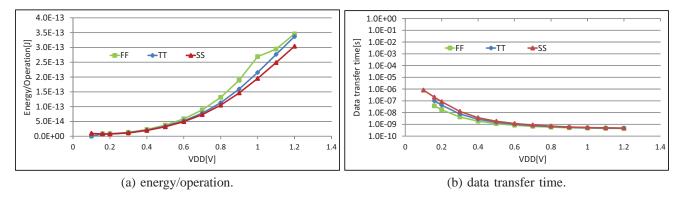

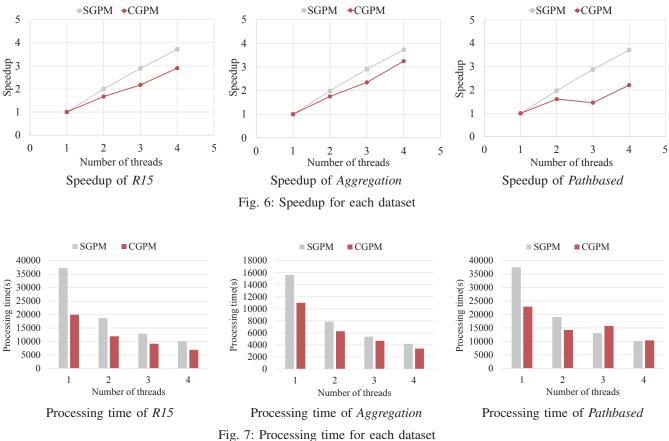

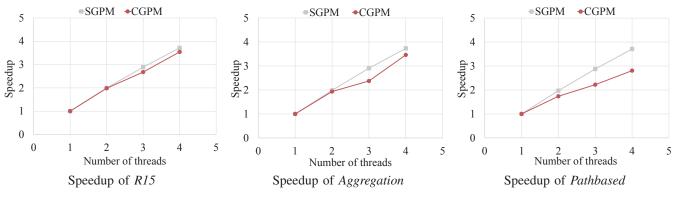

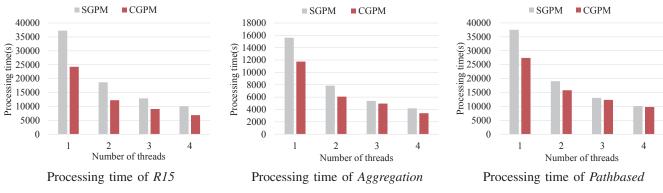

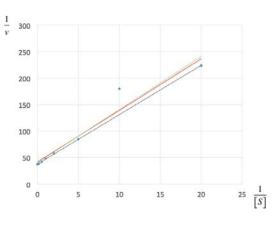

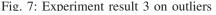

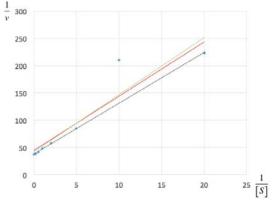

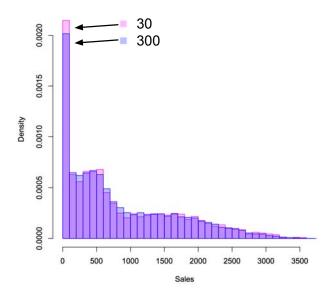

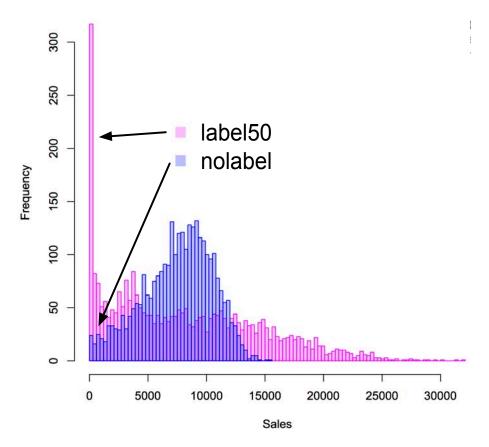

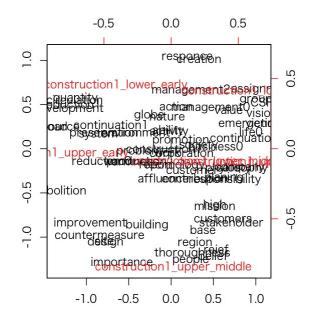

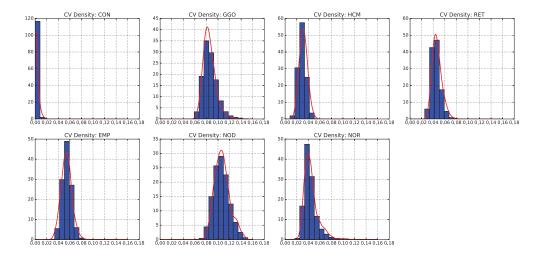

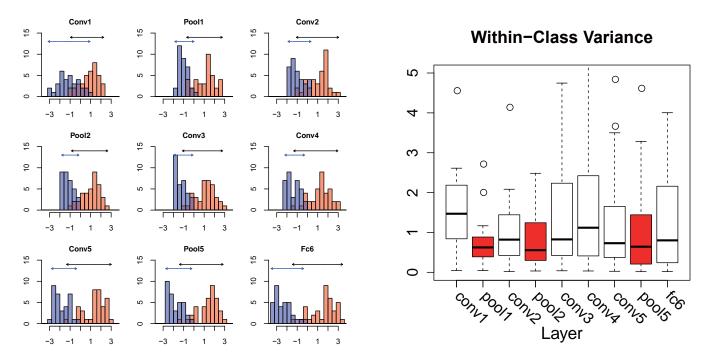

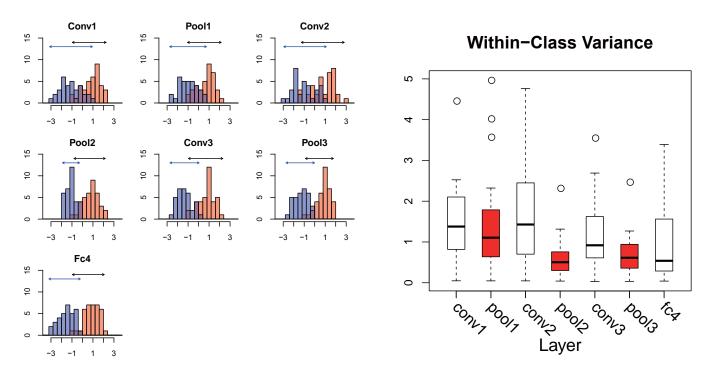

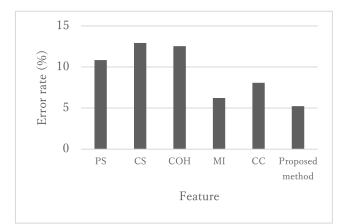

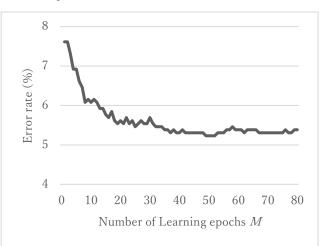

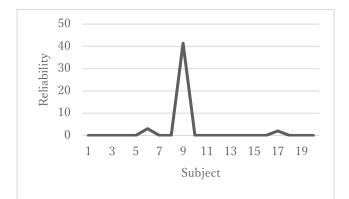

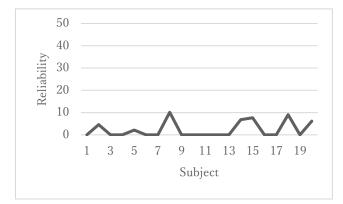

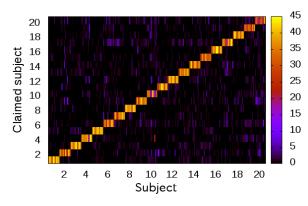

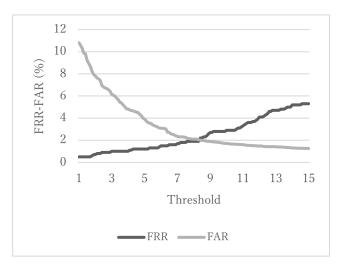

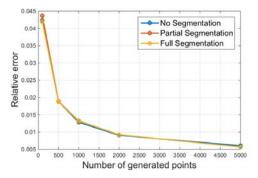

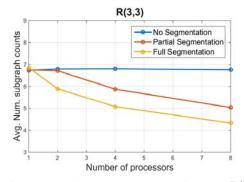

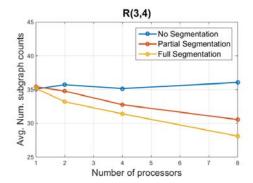

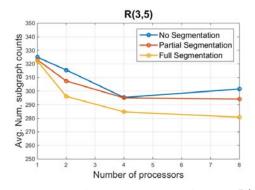

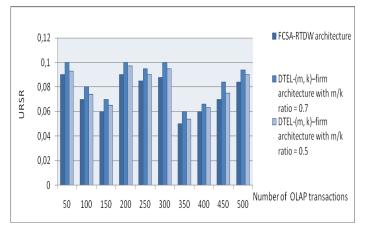

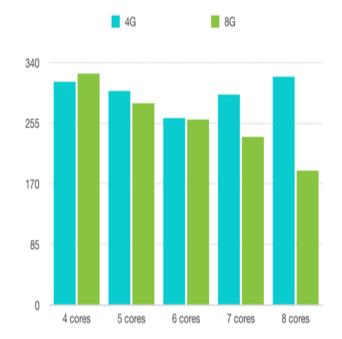

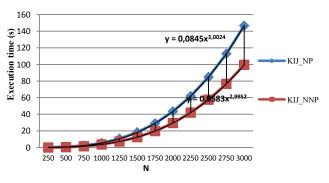

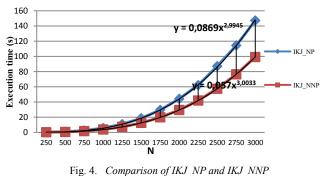

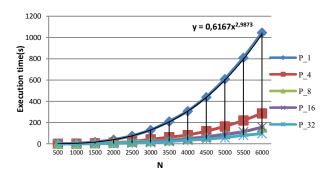

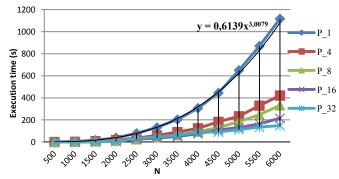

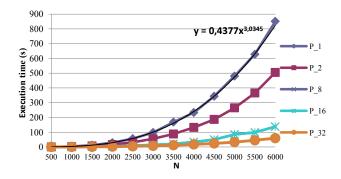

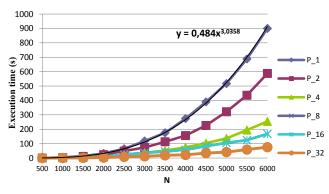

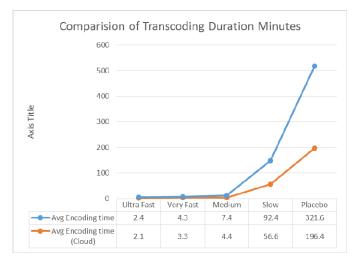

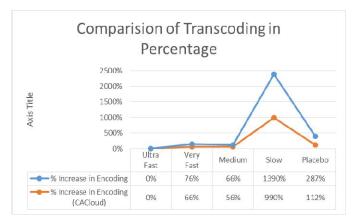

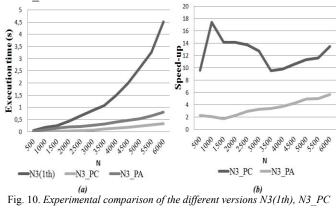

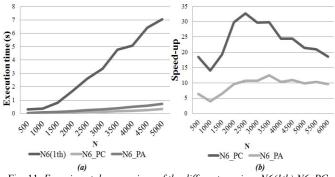

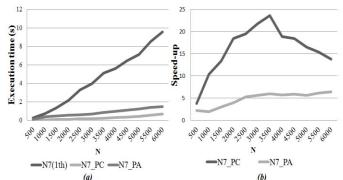

Finally, the design was synthesized on the Kintex FPGA using Xilinx Vivado. The proposed RRM-counting algorithm was compared with a regular summing circuit which is a binary tree of adders (BTA). From the above analysis, it is clear that the RRM-counting will outperform an equivalent circuit of BTA only for large input size. Both circuits (RRM-counting and BTA) are basically combinatorial, and the clock period is measured for one round of computation. The BTA circuit was optimized to use the minimal amount of wires possible to be embedded in the FPGA. Figure 7 depicts the synthesis results for both the restricted RM-counting and the BTA circuits. For the RRM-counting, we used two restrictions on the number of switches a broadcast can traverse  $N^{\frac{1}{k=4}}$ ,  $N^{\frac{1}{k=5}}$ . These results suggest that:

- Only at k = 5 and for  $N = 2^{15}$ , the clock period of the RRM-counting outperforms that of the BTA circuit. This is close to what was predicted by the above analysis, showing that the RRM-counting for sufficiently large values of N, will outperform BTA circuits.

- Observe that the BTA clock period is constantly increasing by 1ns for an increase of 1 in  $\log N$ , while the RRM-counting improves its run-time (for k = 5) by 0.36ns per increase of 1 in  $\log N$ .

- Even when the RRM-counting clock period is longer than that of the corresponding BTA, it is significantly more efficient in terms of power and LUTs, as the RM uses far less logic than the BTA circuit. In particular, note that the BTA for  $N^{16}$  can not fit into the FPGA while the RRM-counting can.

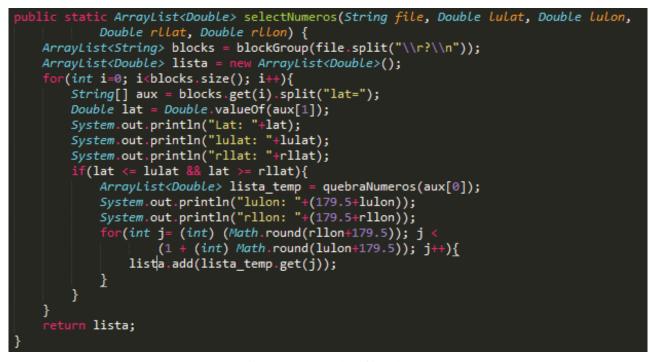

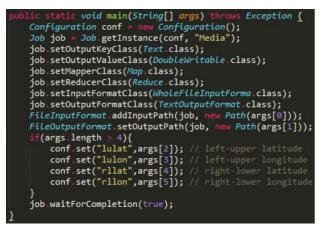

# 5. Verilog coding

The programming style to express RM algorithms is known to be a hard problem. Therefore, describing the Verilog coding of RRM is essential, since it demonstrates a new approach of direct and simple way of coding. Previous work that has addressed this issue, tried to extend C code to include RM processing elements (PEs) and low-level notion of the

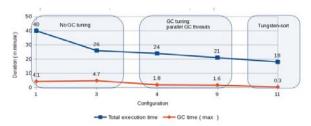

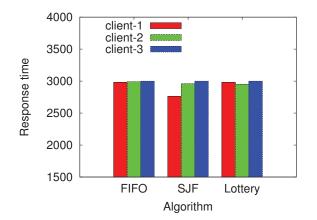

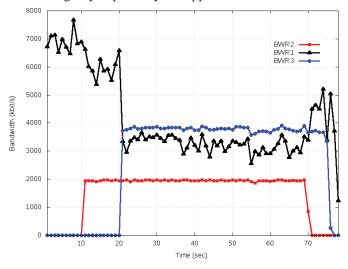

| log N |            | Rmcounting K=4 | Rmcounting K=5 | BTA                 |

|-------|------------|----------------|----------------|---------------------|

|       | Period(ns) | 9.16           |                | 6                   |

| 8     | 8 LUTS 573 |                |                | 665                 |

|       | Power(W)   | 0.051          |                | 0.093               |

|       | Period(ns) |                | 9.4            | 8                   |

| 10    | LUTs       |                | 2026           | 2685                |

|       | Power(W)   |                | 0.171          | 0.258               |

|       | Period(ns) | 17.6           |                | 10                  |

| 12    | LUTs       | 10434          |                | 10831               |

|       | Power(W)   | 0.263          |                | 0.839               |

|       | Period(ns) |                | 11.2           | 12                  |

| 15    | LUTs       |                | 18803          | 87545               |

|       | Power(W)   |                | 0.899          | 1.636               |

|       | Period(ns) | 17             |                |                     |

| 16    | LUTs       | 139059         |                | Too large to handle |

|       | Power(W)   | 1.42           |                |                     |

Fig. 6: FPGA synthesis results

RM-steps. In a RM-step, a PE would: 1-Reconfigure its switch; 2-Broadcast values on its un-connected ports; 3- Read values from its connected ports; 4- Computes new values. Integrating RM-steps into C, created complex programming problems, most of them coordination issues, such as:

- 1) Conditional execution of RM-steps may cause some PEs to execute more RM-steps than the others.

- 2) Recursion and arbitrary function calls involving RMsteps, creates non-equal length RM-steps.

- Inner computations between RM-steps can vary in the amount of instructions that are executed.

- 4) Different RM algorithms use different size of RMs. Should a programmer work with variable or fixed size RMs?

All these problems are hard to solve for a C like programming style due to its serial mode of execution. However, in Verilog (or any other Hardware Description Language) this can be naturally done since it employs a parallel mode of execution wherein clock synchronization is imposed.

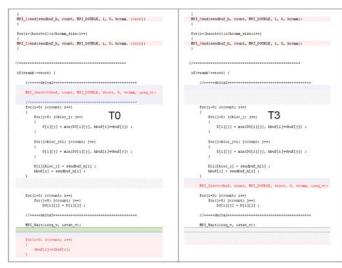

The following code show how simple counting can be programmed in Verilog. First, we define the set of switches needed for the algorithm. For simple counting, we need only one type of switch that have two states: a band  $\langle W \Longrightarrow N$ ,  $S \Longrightarrow E >$  or horizontal-pass  $\langle W \Longrightarrow E$ , S, N >. The control of this switch is done by the input bit x which is directly fed to the switch. We use bufif1 tristate devices to implement this switch.

```

module SW (x, w, s, e , n);

input w,s,x;

output e,n;

tri e,n;

bufif1 bwn(n, w, x);

bufif1 bse(e, s, x);

bufif1 bwe(e, w, ~x);

endmodule

```

Next, we define the module that creates a complete  $8 \times 8$  RM. We mainly use the generate – for construct to create a two dimensional array of switches. The input bits are passed

to the module via an array of N = 8 wires inp[...]. The x parameter of each switch will be assigned the suitable input bit when this switch is instantiated by the generate – for construct. Thus, the following code (for one dimension of the RM) will create/instantiate six switches  $s_1, \ldots, s_6$  with the suitable input bit inp[X].

```

genvar X,Y;

generate

for (X=1; X < N-1; X=X+1)

SW        s (inp[X],...);

```

Next, when a switch  $s_X$  is instantiated, its W-port needs to be connected to  $s_{X-1}$ 's E-port. This is done by declaring an array  $WLR[\ldots]$  of wires and connecting to the E-port of  $s_{X-1}$  to the W-port of  $s_X$  via a wire WLR[X-1] as follows:

```

wire WLR [0:N-1];

genvar X,Y;

generate

for (X=1; X < N-1; X=X+1)

SW s(inp[X],WLR[X-1],...,WLR[X][Y],...);

```

Since the RM is two dimensional, we need to connect  $s_{X,Y}$ 's E-port to  $s_{X-1,Y}$ 's W-port and  $s_{X,Y}$ 's S-port to  $s_{X,Y-1}$ 's N-port. Thus, full connections are obtained using 2D arrays of wires as follows:

```

wire WLR [0:N-1][0:N];

wire WUD [0:N-1][0:N];

genvar X,Y;

generate

for (X=1; X < N-1; X=X+1)

for (Y=1; Y < N; Y=Y+1)

SW s(inp[X],WLR[X-1][Y],

WUD[X][Y-1],WLR[X][Y],WUD[X][Y]);

```

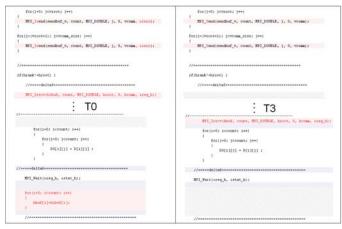

Creating The overall RM is more complicated since the external edges of the RM form the ends and should be instantiated differently than the internal switches of the RM. The following module instantiate a full RM using separate generate -for statements for the edges and separate instantiations for the corners of the RM.

```

module RMcounting #(parameter N=8)(inp,out);

input inp;

output out;

wire [0:N-1] inp;

wire [0:N]

out;

wire WLR [0:N-1][0:N];

wire WUD [0:N-1][0:N];

genvar X,Y;

generate

for (X=1; X < N-1; X=X+1) begin

for (Y=1; Y < N; Y=Y+1) begin

SW s(inp[X],WLR[X-1][Y],

WUD[X][Y-1],WLR[X][Y],WUD[X][Y]);

end end endgenerate

generate for (Y=1; Y < N; Y=Y+1) begin

SW sl(inp[0],1'b0,WUD[0][Y-1],

WLR[0][Y], WUD[0][Y]);

end endgenerate

generate for (Y=1; Y < N; Y=Y+1) begin

SW sr(inp[N-1],WLR[N-2][Y],

WUD[N-1][Y-1], out[Y], WUD[N-1][Y]);

end endgenerate

```

```

generate for (X=1; X < N-1; X=X+1) begin

SW sd(inp[X],WLR[X-1][0],

1'b0,WLR[X][0],WUD[X][0]);

end endgenerate

generate for (X=1; X < N-1; X=X+1) begin

SW su(inp[X], WLR[X-1][N],

WUD[X][N-1],WLR[X][N],WUD[X][N]);

end endgenerate

SW s00(inp[0],1'b1,1'b0,WLR[0][0],WUD[0][0]);

SW sON(inp[0],1'b0,WUD[0][N-1],

WLR[0][N],WUD[0][N]);

SW sN0(inp[N-1],WLR[N-2][0],1'b0,

out[0],WUD[N-1][0]);

sNN(inp[N-1], WLR[N-2][N],

SW

WUD[N-1][N-1], out[N], WUD[N-1][N]);

endmodule

```

# 6. Conclusion

In this paper we presented the RRM wherein broadcasting along buses is restricted not to pass through more than  $d(n) = n^{\frac{1}{k}}$  switches, where k = 2, 3, ... and n is the input size. We argued that using the RRM, the theoretical broadcast assumption of O(1) is feasible, using current transistors technology. We have shown that the fundamental problem of counting can be done on the RRM in 2k steps. An almost matching lower bound was presented, showing that the RRM can not compute counting in less than k + 1steps. Finally, we presented a realization of the counting algorithm, coded directly in Verilog. We demonstrated that RM algorithms can be directly synthesized to circuits using hardware description language even for large size of RMs, while previous realizations of the RM were mainly to a smallsize grid of Soft-CPUs using MUX-gates for reconfiguration, which cannot scale well. The Verilog realization of the RRM is shown to outperform a regular optimal parallel adderscircuit both for current CMOS technology and Optical ring resonators. This work thus presents a significant step toward a realization of the RM algorithms.

# References

- Y. Ben-Asher and A. Schuster. The bus-usage method for the analysis of reconfiguring networks algorithms. In *Proc. of the Intl. Parallel Processing Symp.*, Beverly Hills, March 1992.

- [2] Yosi Ben-Asher, Dan Gordon, and Assaf Schuster. Efficient self simulation algorithms for reconfigurable arrays. In *AlgorithmsâĂŤESA'93*, pages 25–36. Springer, 1993.

- [3] Yosi Ben-Asher, David Peleg, and Assaf Schuster. The complexity of reconfiguring network models. In *Israel Symposium on Theory of Computing Systems*, pages 79–90, 1992.

- [4] Bryan Beresford-Smith, Oliver Diessel, and Hossam ElGindy. Optimal algorithms for constrained reconfigurable meshes. *Journal of Parallel* and Distributed Computing, 39(1):74–78, 1996.

- [5] G. Chen, B. Wang, and H. Li. Deriving algorithms on reconfigurable networks based on function decomposition. *Theoretical Computer Science*, 120(2):215–27, November, 1993.

- [6] J. L. Trahan C.P.Subbaraman and R. Vaidyanathan. List ranking and graph algorithms on the reconfigurable multiple machine. In *Proceedings of International Conference on Parallel Processing, pages III–224–247. CRC Press, August,* 1993.

- [7] D. Ding and D. Z. Pan. Oil: a nano-photonics optical interconnect library for a new photonic networks-on-chip architecture. In *Proceed*ings of the 11th international workshop on System level interconnect prediction, 2009.

- [8] Hatem M El-Boghdadi, Ramachandran Vaidyanathan, Jerry L Trahan, and Suresh Rai. On the communication capability of the selfreconfigurable gate array architecture. In *ipdps*, page 0152b. IEEE, 2002.

- [9] W. C. Elmore. The transient response of damped linear networks with particular regard to wideband. *Journal of Applied Physics*, 19:55–63, 1948.

- [10] Heiner Giefers and Marco Platzner. Armlang: a language and compiler for programming reconfigurable mesh many-cores. In *Parallel & Distributed Processing*, 2009. IPDPS 2009. IEEE International Symposium on, pages 1–8. IEEE, 2009.

- [11] Heiner Giefers and Marco Platzner. An fpga-based reconfigurable mesh many-core. 2013.

- [12] J. Jang, H. Park, and V.K. Prasanna. An optimal multiplication algorithm on reconfigurable mesh. In *Proc. Symp. on Parallel and Distributed Processing*, pages 381–391, 1992.

- [13] J. Jang and V.K. Prasanna. An optimal sorting algorithm on reconfigurable mesh. In *Proc. Inter. Parallel Processing Symp.*, pages 130–137, March 1992.

- [14] Ju-wook Jang and Viktor K. Prasanna. An optimal sorting algorithm on reconfigurable mesh. In *Proceedings of 6th International Parallel Processing Symposium, pages 130–137. IEEE*, 1992.

- [15] Y. Matias and A. Schuster. On the power of a 2-band reconfigurable network. Unpublished Manuscript, 1992.

- [16] R. Miller, V.K. Prasanna-Kumar, D.I. Reisis, and Q.F. Stout. Image computations on reconfigurable VLSI arrays. In *Proceedings of the Conference on Vision and Pattern Recognition*, pages 925–930, 1988.

- [17] K. Nakano and K. Wada. Integer summing algorithms on reconfigurable meshes. *Theoretical Computer Science, Vol. 197, pp. 57–77, Jan*, 1998.

- [18] Madhusudan Nigam and Sartaj Sahni. Sorting n numbers on n× n reconfigurable meshes with buses. *Journal of Parallel and Distributed Computing*, 23(1):37–48, 1994.

- [19] Stephan Olariu, James L. Schwing, and Jingyuan Zhang. Fast component labeling and convex hull computation on reconfigurable meshes. *Image and Vision Compututing*, 11(7):1993, September, 1993.

- [20] Oday Abdul Lateef Abdul Ridha. Performance estimation of n-bit classified adders. 2013.

- [21] Reetinder Sidhu, Sameer Wadhwa, Alessandro Mei, and Viktor K Prasanna. A self-reconfigurable gate array architecture. In *Field-Programmable Logic and Applications: The Roadmap to Reconfigurable Computing*, pages 106–120. Springer, 2000.

- [22] JL Trahan and R Vaidyanathan. Relative scalability of the reconfigurable multiple bus machine. In Proc. Workshop Reconfigurable Arch. and Algs, 1996.

- [23] Biing-Feng Wang and Gen-Huey Chen. Constant time algorithms for the transitive closure and some related graph problems on processor arrays with reconfigurable bus systems. *IEEE Transactions on Parallel* and Distributed Systems, 1(4):500–507, October, 1990.

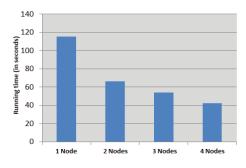

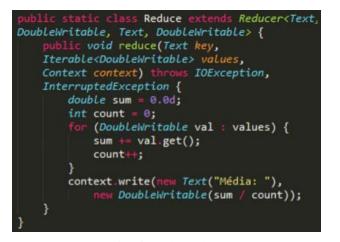

# Hardware Implementation of Parallel Algorithm for Setting Up Benes Networks

Yikun Jiang and Mei Yang Department of Electrical and Computer Engineering University of Nevada, Las Vegas Emails: jiangy3@unlv.nevada.edu, Mei.Yang@unlv.edu

Abstract— Benes/Clos networks have been used in many areas, such as interconnection network in parallel computers, multiprocessors system, and networks-on-chip. The parallel switch setting algorithm is the key to satisfy the requirements of high performance switching networks. The Lee's routing algorithm is by far the most efficient parallel routing algorithm for Benes networks. However, there is no hardware implementation for this algorithm. In this paper, the Lee's routing algorithm is fully implemented in RTL and synthesized. We have refined the algorithm in data structure and initialization/updating of relation values to make it suitable for hardware implementation. The simulation and synthesis results of the switching setting circuits for 8x8 to 32x32 Benes networks confirm that the timing, area, and power consumption of the circuit is consistent with the complexity of the Lee's algorithm. To the best of our knowledge, this is the first complete hardware implementation of the parallel switch setting algorithm which can handle all types of permutations including partial ones.

# Keywords— Benes, Parallel Algorithm, Hardware, RTL, Implementation, Synthesis

### I. INTRODUCTION

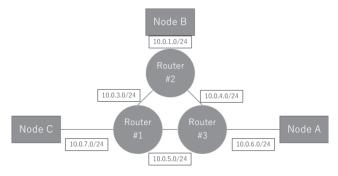

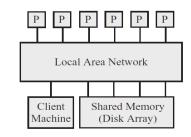

Both Benes and Clos networks are rearrangeably non-blocking multi-stage interconnection networks. Benes network is a special case of Clos network which has  $N = 2^n$  inputs and outputs. The Benes network is constructed with  $2 \times 2$ switching nodes recursively. Due to their non-blocking property and relative smaller number of crosspoints, Benes/Clos networks have received much attention in both academia and industry. Benes/Clos networks have been used in many areas, such as interconnection network in parallel computers, multiprocessors system [1], and networks-on-chip [2][3][4][12][13]. In packet switching systems, the switch fabric must be able to provide internally conflict-free paths for the requesting packets in each time slot [5]. This is implemented by setting the states of all switches in the network. It is clear that the routing assignment (i.e., switch setting) scheme in Benes/Clos networks has a strong impact to the efficiency of the Bene/Clos networks.

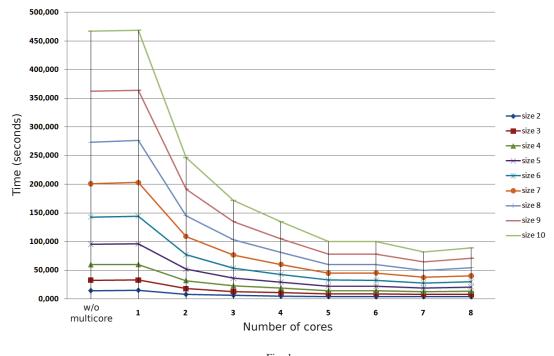

A number of switch setting algorithms have been developed in the past few decades, including sequential algorithms and parallel algorithms. Sequential algorithms such as looping algorithms [7] are designed for circuit switching systems where the switching configuration can be rearranged at relatively low speed. In [7], a switch setting algorithm with time complexity O(NlogN) is proposed based on Waksman's proof. As a matter of fact, using sequential algorithm, the  $N \times N$  Benes network cannot be set up in less than O(NlogN) time, because there are O(NlogN) switches. The set-up time is much longer than the latency in Benes networks, which is O(logN) for  $N \times N$  network. In order to obtain a switch setting algorithm of complexity comparable to the network latency, parallel algorithms are needed.

In [9], Nassimi and Sahni developed a parallel set-up algorithm which runs significantly faster than the sequential algorithm based on Waksman's proof. The complexity of this algorithm depends on the parallel computer model and the number of processing elements available. Four SIMD models with different topologies are studied: Completely Interconnected Computer (CIC) with time complexity of  $O(log^2N)$ , Mesh-Connected Computer (MCC) with time complexity of  $O(\sqrt{N} \log^2 N)$ , Cube Connected Computers (CCC) with time complexity of  $O(log^4N)$ , and Perfect Shuffle Computer (PSC) with time complexity of  $O(log^4N)$ . The time complexity of topologies other than CIC is fairly high. However, CIC is simply too complex to be realized. In addition, this parallel algorithm [9] cannot handle the partial permutations. The authors also proposed a self-routing algorithm for Benes network [9] to route through the network using destination tags. However, this algorithm cannot route all permutations.

In [5][11], Lee and Liew present a parallel routing algorithm for Benes Networks. It has time complexity  $O(log^2 N)$  which is same as CIC but using only N/2processing elements [9]. This algorithm was developed based on the previous work in [8] and [9], but can handle the partial permutation problem. In addition, the algorithm can be extended and applied to Clos networks with two's power number of central modules. In the literature, there is nearly no hardware implementation of this parallel algorithm. In [3], a simple hardware design based on Lee's algorithm for  $16 \times 16$ Benes network in FPGA is presented. However, no detailed design and simulation results are shown in that paper. Another problem about [3] is that, the work is only limited to the switch setting unit for the first stage of  $16 \times 16$  Benes network. Without the design of the switch setting circuit for different size networks, there is no way to tell the trend of how the hardware cost would increase correspondingly when the network size grows.

In this paper, we present the hardware design of Lee's parallel routing algorithm for Benes networks in different

sizes ranging from  $8 \times 8$  to  $32 \times 32$ . The algorithm is refined to make it more suitable for hardware design. The Register-Transfer-Level (RTL) design of the algorithm is coded in Verilog, simulated, and synthesized using Cadence tools under 65nm technology. The timing delay trend is consistent with the time complexity trend of Lee's algorithm. The switch setting hardware design can be integrated with Benes network circuit to be used in high-performance network-on-chip systems.

The rest of the paper is organized as follows. Section II presents the parallel routing algorithm. Section III presents the RTL design and improvement of Lee's parallel routing algorithm. Section IV presents the synthesis results and analysis of the results.

### II. LEE'S PRALLEL ROUTING ALGORITHM

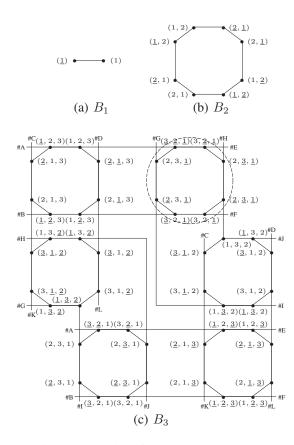

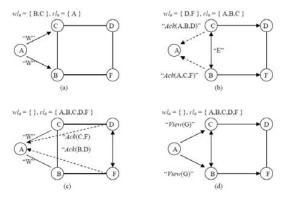

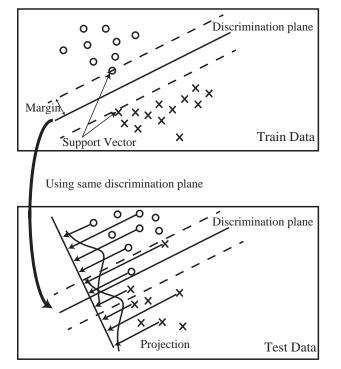

### A. Lee's Algorithm

Lee's parallel algorithm can be decomposed into four major steps: initialization, searching, merging and calculating the permutation for subnetworks. Denote the set of input and output ports as I and O, respectively, i.e., I = O = $\{0, 1, ..., N - 1\}$ , and  $\pi: I -> O$  be an input-output permutation indicating connection requests. We use (i, j) to indicate the *i*th input port is going to connect to the *j*th output port in the permutation. In this part, we will use an example permutation to elaborate the main concept of this algorithm. In the below permutation, 'X' means this input port has no output request.

$$\pi = \begin{pmatrix} 0 & 1 & 2 & 3 & 4 & 5 & 6 & 7 \\ 0 & 3 & 2 & 6 & 4 & 7 & 5 & X \end{pmatrix}$$

Because of the symmetric routing constraint, the algorithm only need to find out the routing bits of the stages in one Omega subnetwork, then the routing bits of the counterpart stages in the other Omega network will be determined. In Lee's algorithm, the output side switch setting is determined first, then the input side switch setting is derived.

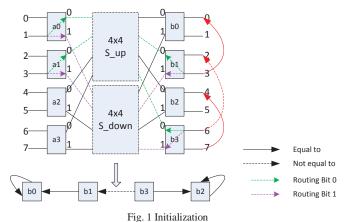

### B. Initialization

The first step of Lee's algorithm is to build the connections between output switching nodes using relation values. The connection between output switching nodes are built on the internally conflict-free constraint, to avoid this internal conflict, the algorithm need to group switching nodes with the same relation together, and assign the switch state values to them consistently.

Here, we adopt the same notations as in (Lee et al., 1996). We use  $a_i$  and  $b_i$  to denote the switch state value of input/output switching node  $a_i$  and  $b_i$ , respectively. Let  $\alpha: I \to \{0, 1\}$  and  $\beta: O \to \{0, 1\}$ , where  $\alpha(k)$  is the routing bit of *k*th input, and  $\beta(k)$  is the routing bit from *k*th output.

From [5], the symmetric self-routing constraint requires that

$$\alpha(k) = \beta(\pi(k)) \qquad k=0, 1, ..., N-1 \quad (1)$$

The internal conflict-free constraint requires that

$$\alpha(k) = \overline{\alpha}(k+1), \ \beta(k) = \overline{\beta}(k+1) \ k=0, 1, ..., N-2$$

(2)

The combination of (1) and (2) gives \_\_\_\_

$$\beta(\pi(k)) = \alpha(k) = \overline{\alpha}(k+1) = \overline{\beta}(\pi(k+1))$$

$$k=0, 1, ..., N-2 \qquad (3)$$

Fig. 1 III Then we have

$$\alpha_{i} = \begin{cases} \frac{a_{k}}{2}, \ k \ is \ even \\ \frac{\overline{a_{k-1}}}{2}, \ k \ is \ odd \\ \frac{b_{k}}{2}, \ k \ is \ even \\ k = 2i \end{cases}$$

(4)

$$\beta_i = \begin{cases} \frac{2}{b_{k-1}}, & k \text{ is odd} \\ k = 2i+1 \end{cases}$$

(5)

For the given permutation, we have:

$$\pi = \begin{pmatrix} 0 & 1 & 2 & 3 & 4 & 5 & 6 & 7 \\ 0 & 3 & 2 & 6 & 4 & 7 & 5 & X \end{pmatrix} => \\ \begin{pmatrix} a_0 & \overline{a_0} & a_1 & \overline{a_1} & a_2 & \overline{a_2} & a_3 & \overline{a_3} \\ b_0 & \overline{b_1} & b_1 & b_3 & b_2 & \overline{b_3} & \overline{b_2} & X \end{pmatrix}$$

For the *i*th input switching node, we refer to the output port pair (k, l) corresponding to the input port pair (2i, 2i + 1) as a *connection pair*. Then we obtain:

$$\begin{pmatrix} 2i & 2i+1 \\ k & l \end{pmatrix} => \begin{pmatrix} a_i & \overline{a_i} \\ \beta(k) & \beta(l) \end{pmatrix}$$

Based on Eqn. (3), we have:

$$\beta(k) = \overline{\beta(l)} \tag{6}$$

Consider the given permutation, taking (1, 3) as example. As shown in Fig. 1, in order to have the same routing bits ('0' or '1') for input port 1 and output port 3, the corresponding input switching node must set the state value base on the corresponding output switching node, i.e., for input/output permutation  $\binom{1}{3}$ , we have  $\alpha(1) = \overline{a_0}$ ,  $\beta(3) = \overline{b_1}$ , since  $\alpha(1) = \beta(3)$ , then we can get  $a_0 = b_1$ . Similarly, for  $\binom{3}{6}$ , we derive,  $\overline{a_1} = b_3$ . Together, we obtain

After eliminating all a from above equations, we can obtain a set of N/2 initializing equations as follows:

$b_1 = b_0, \ b_3 = b_1, \ b_3 = b_2, \ b_2 = X$

These equations about b can help us to build the relation connections between output switching nodes as shown in Fig. 1. All output switching nodes are connected like a linked list, where the index of the state variable is taken as the node

address. Each initializing equation is used to establish a pointer, in which the state variable with larger index points to the other with smaller index.

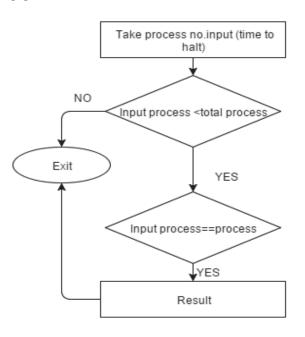

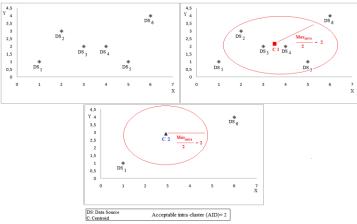

After initialization step, all output switching nodes can be grouped into equivalent classes. For switching nodes in the same class, the state value of any switching node is relevant to the state value of others. The *representative node* of each class is the switching node with the smallest index number. For the above example, as shown in Fig. 1, all output switching nodes are in the same class. The representative node of the group is  $b_0$ . Regardless of the Benes network radix, the initialization step is processed at all PEs at the same time with time complexity O(1).

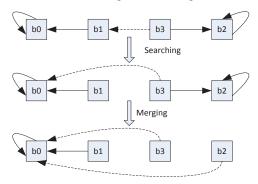

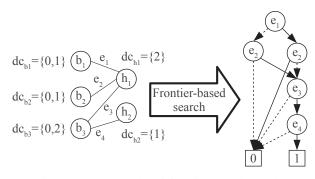

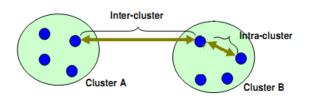

#### C. Searching

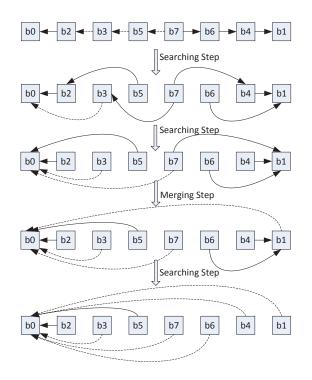

As shown in Fig. 1, there are two pointer types, Type 0 Pointer indicating the two state variables are equal, and Type 1 Pointer indicating the two state variables are not equal. All switching nodes except the representative node in the group will go through the searching step to point to the representative node. The time complexity of searching step is O(logN).

Fig. 2 shows the searching result for Fig. 1.

Fig. 2 Searching and Merging

#### D. Merging

Usually, among the nodes belonging to the same class, there should be only one endpoint which is the representative node of the class. If there are two endpoints in one class, then the merging step is needed to eliminate one of them. The time complexity of this merging step is O(1). Fig. 2 shows that the two endpoints  $b_0$  and  $b_2$  are pointed by  $b_3$ , which means the value of  $b_3$  will be determined by the values of  $b_0$  and  $b_2$ , causing confliction. As shown in Fig. 2, after the merging step, the direct connection between two endpoints  $b_0$  and  $b_2$  is found.

After all switching nodes point to the representative of the class, the state values of all switching nodes can be determined by assigning the state value of the representative as 0 or 1. One of the assignments of the above example is derived as by letting  $b_0 = 0$ :

*State*  $(b_0, b_1, b_2, b_3) = (0, 0, 1, 1)$

By applying the symmetric routing constraint, the state values of input switching nodes should be setup as:

State

$$(a_0, a_1, a_2, a_3) = (0, 0, 1, 0)$$

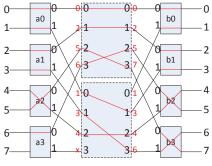

Fig. 3 shows the settings of input/output switching nodes for the given permutation  $\pi$ .

### E. Permutation for Subnetworks

After the state values of input/output switching nodes are determined, the switch settings of two inner  $\frac{N}{2} \times \frac{N}{2}$  subnetworks can be determined recursively. The permutations of the two inner subnetworks can be derived by tracing the routing paths from both input and output sides. Then Lee's algorithm is applied to derive the state values of the input/output switching nodes of the two subnetworks. The time complexity to calculate those permutations for subnetworks is O(1). In a recursive manner, the state values of all stages will be computed by the Lee's parallel routing algorithm.

Fig. 3 Permutation for Subnetwork

Fig. 3 shows the connections of the two inner subnetworks and the derived two permutations  $\pi_0$  for  $S_{up}$  and  $\pi_1$  for  $S_{down}$  for two inner subnetworks, respectively.

$$\pi_0 = \begin{pmatrix} 0 & 1 & 2 & 3 \\ 0 & 1 & 3 & 2 \end{pmatrix}, \pi_1 = \begin{pmatrix} 0 & 1 & 2 & 3 \\ 1 & 3 & 2 & x \end{pmatrix}.$$

Continue this process until the state values of the middle stage switching nodes are determined.

As we can see from the description in above section, the searching step is the only procedure which is relevant to the radix of Benes network. All the other procedures could be finished in O(1). The time complexity for each round is determined by the searching procedure which is O(logN).

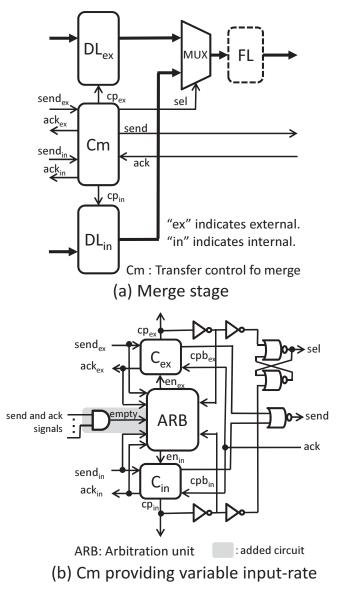

#### III. HARDWARE DESIGN OF LEE'S ALGORITHM

### A. Design Flow

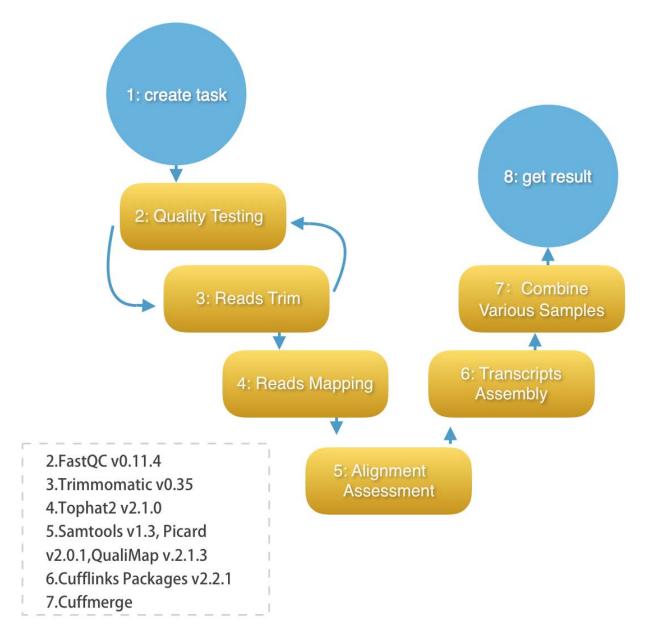

The hardware design of Lee's algorithm follows the common RTL design flow which consists of four steps: 1) specification, 2) RTL design, 3) simulation of the RTL code, 4) synthesis of the RTL design. In the second step, we use Verilog HDL to implement the RTL design of Lee's parallel algorithm.

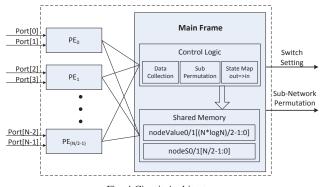

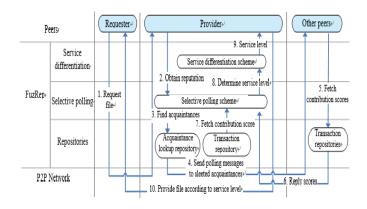

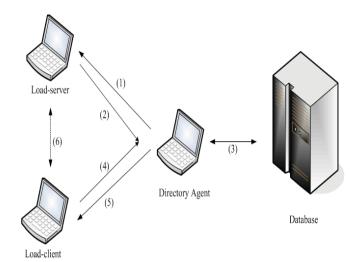

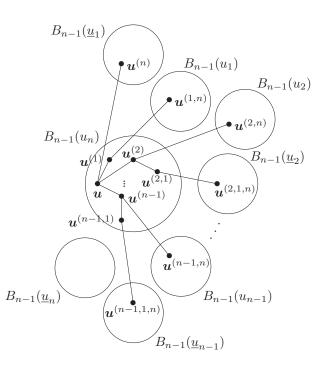

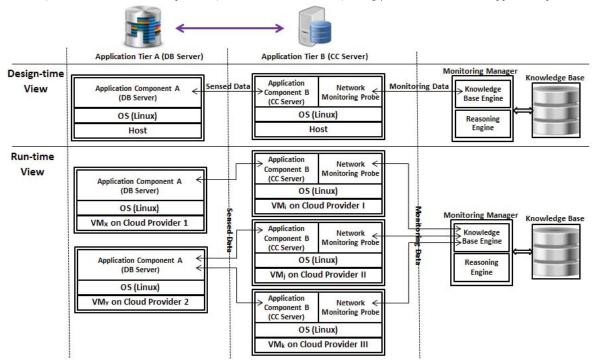

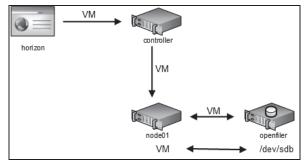

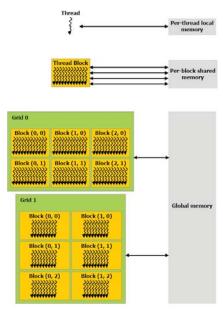

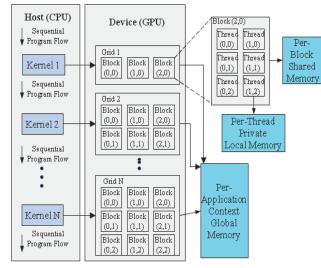

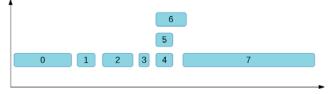

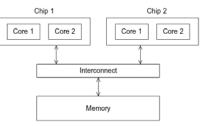

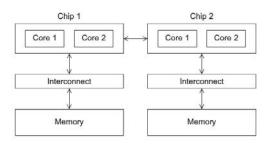

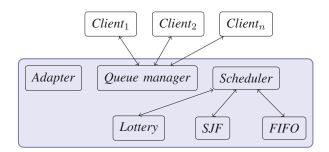

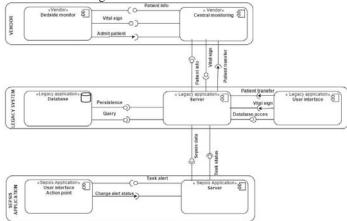

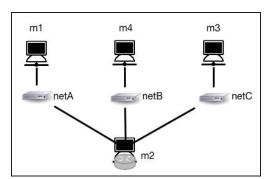

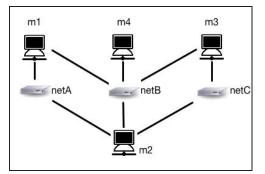

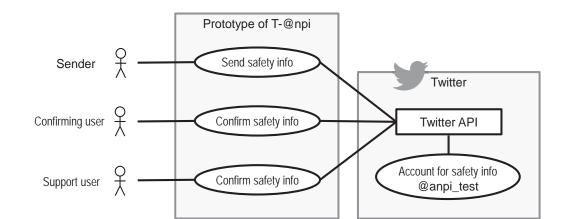

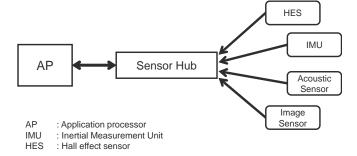

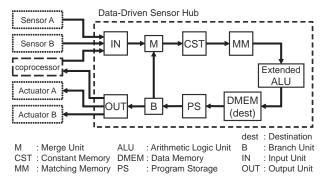

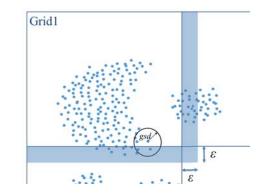

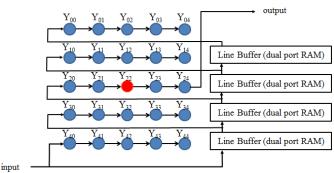

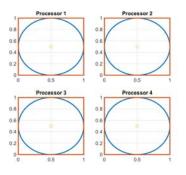

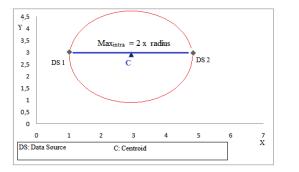

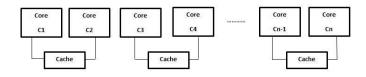

As shown in Fig. 4, the switch setting circuit of  $N \times N$ Benes network takes the input of N output port indexes representing the permutation and generates the switch setting of every two stages as well as the permutation of two inner  $\frac{N}{2} \times \frac{N}{2}$  subnetworks. There are N/2 processing elements (PE), each representing an output switching node, are connected by the main frame. Each  $P_i$  holds several variables. In the main frame, two major parts are the control logic and shared memory. TABLE I. lists the variables used in our design. For  $N \times N$  Benes network, each variable storing port index has  $n = log_2^N$  bits. The global variables are shared among all processing elements.

Fig. 4 Circuit Architecture

As each output switching node (represented by one processing element) has two ports, 0 and 1, we adopt a tworegister structure for each output switching node to store the pointers associated with port 0/1. In the searching step of Lee's algorithm, each PE may need search in two directions. The two-register structure allows each PE keeps searching in two directions until they reach the representative nodes. Here four variables are used for storing the index of the node (nodeValue0/1) pointed by the port 0/1 pointer and corresponding relation value (nodeS0/1), respectively. The size of these shared registers is determined by the radix of Benes network. For  $N \times N$  Benes network, the size of nodeValue0/1 is (N/2) \* logN bits as there are N/2 output switching nodes and logN bits are needed to represent the index of each port. The size of nodeS0/1 is N/2 as one bit is needed to represent the relation value between two connected switching nodes, '0' represents not equal, '1' represents equal.

TABLE I. DEFINITION OF VARIABLES

| Global Variable                              | Meaning                                                                                                                                                                                                                                                                                                                  | Size (bit) |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| port[N]                                      | Store the output port index of the permutation.                                                                                                                                                                                                                                                                          | NlogN      |

| nodeValue $0/1[\frac{N}{2}]$                 | Store the index of the port<br>which is pointed by the port<br>0/1 pointer of each output<br>switching node. For example,<br>nodeValue $0/1[i] = j$ ,<br>$0 \le j \le i \le N/2$ , means<br>node <i>i</i> points to node <i>j</i> , i.e.,<br>there is a relation connection<br>between node <i>i</i> and node <i>j</i> . | NlogN<br>2 |

| nodeS0/1                                     | Store the relation value for<br>the connection from the port<br>0/1 pointer of each output<br>switching node.                                                                                                                                                                                                            | N/2        |

| inNodeStateValue[ $\frac{N}{2}$ ]            | Store the state value of input switching nodes.                                                                                                                                                                                                                                                                          | N/2        |

| outNodeStateValue $\left[\frac{N}{2}\right]$ | Store the state value of output switching nodes.                                                                                                                                                                                                                                                                         | N/2        |

| $sub0/1\_port[\frac{N}{2}]$                  | Store the permutations for two inner subnetworks.                                                                                                                                                                                                                                                                        | logN/2     |

| Local Variable                               | Meaning                                                                                                                                                                                                                                                                                                                  | Size (bit) |

| port0/1                                      | Stores the output port index<br>of the connection pair<br>corresponding to input port<br>pair $(2i, 2i + 1)$ .                                                                                                                                                                                                           | logN       |

| preNodeValue0/1                              | Stores the nodeValueL0/1<br>before each searching                                                                                                                                                                                                                                                                        | logN       |

|          | procedure.                                                                                                                                                               |   |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| nodeType | Two-bit value, '00' means the<br>node doesn't point to any<br>other node; '01' if the node<br>points to only one other node,<br>'11' if it points to two other<br>nodes. | 2 |

The control logic is responsible for the following functions:

- 1. Maintaining and updating the registers' data and status respectively, according to the newest information received from processing elements.

- 2. Calculating the setting value for switching nodes on the inputs/outputs stage.

- 3. Calculating the input/output permutation for the subnetworks.

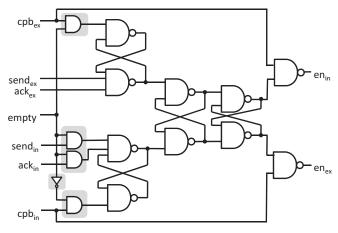

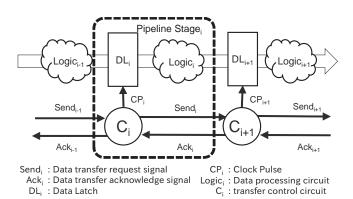

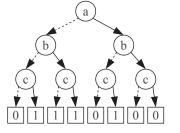

#### B. Finite State Machine

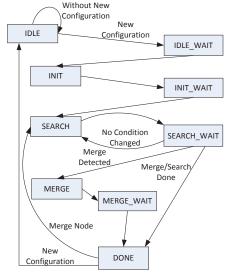

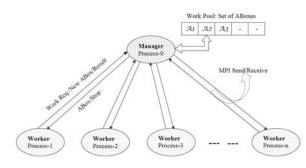

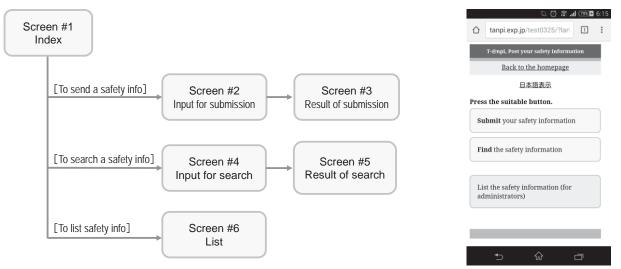

In this part, the RTL design of Lee's parallel algorithm is presented. Following the process of Lee's parallel routing algorithm, we derive the finite state machine of each processing element as shown in Fig. 5 which encloses five steps: 1) IDLE, 2) INIT, 3) SEARCH, 4) MERGE, 5) DONE.

Each step could be divided into several states to complete the function that this step is supposed to do. Those states named with 'WAIT' as appendix are used to synchronize processing elements. All the processing elements need to wait one clock cycle so that the register values updated by other processing elements become valid in all processing elements. In the following part of this section, we will describe these five main steps.

Fig. 5 State Diagram

### **IDLE**

At the starting point, all processing elements are in the IDLE state to wait for the new permutation between input and output ports. When the new permutation arrives by setting input ports of all input switching nodes, all processing elements will enter the INIT state to conduct initialization functions. Before the processing element enters the INIT state, the control unit needs one clock cycle to synchronize with all other processing elements.

In the IDLE state, all register values are reset to default values, where nodeValue0/1 and preNodeValue0/1 are set to the current node index and nodeS0/1 are all reset to 0.

### INIT

In Lee's parallel routing algorithm, the first step is to initialize the pointers and relation values between output switching nodes. This initialization process is determined by the permutation between inputs and outputs of Benes network. Consider the following permutation for a  $16 \times 16$  Benes network:

```

\pi = \begin{pmatrix} 0 & 1 & 2 & 3 & 4 & 5 & 6 & 7 & 8 & 9 & 10 & 11 & 12 & 13 & 14 & 15 \\ 10 & 14 & 9 & 2 & 8 & 13 & 12 & 15 & 1 & \times & 7 & 11 & 5 & 0 & 4 & 6 \end{pmatrix}

```

There are two types of relation between two output switching nodes that have connection, equal or not equal, represented as '0' or '1' respectively. In Lee's parallel routing algorithm, in order to find out the relation between these two output switching nodes, the equations between routing bits of input/output switching nodes need be derived first. In our design, the relation between two output switching nodes can be derived directly from the parity of two output port indexes corresponding to the two input ports of each PE.

Given the connection pair (k, l) for an input port pair (2i, 2i + 1) (i.e., port0 and port1 in our design), according to Eqns. (4), (5) and (6), we derive the four possibilities of the above equation:

Case 1: k is even and l is even, we have  $b_k = \overline{b_l};$ Case 2: k is even and l is odd, we have

opposite odd-even property, then their corresponding output switching nodes will have the same state value, otherwise, they have the opposite state value. The relation between two output switching nodes can be set according to odd-even property of k and l by checking port0[0] and port1[0] as shown in Eqn. (3).

$$NodeS0/1 = \sim (port0[0] XOR port1[0]) = \begin{cases} 0 & Equal \\ 1 & Not Equal \end{cases}$$

(7)

At each processing element  $P_i$ , the following code is used to set nodeValue0/1 and NodeS0/1, where  $n = log_2^N$ .

*II pNode is the temporal variable to hold the larger node index* if (port0[n-1:1] < port1[n-1:1])pNode = port1[n - 1:1];*if* (*port*1[0]) { nodeValue1[pNode] = port0[n - 1:0];nodeS1[pNode] = (port0[0] == port1[0])? 1'b1 : 1'b0;} else { nodeValue0[pNode]] = port0[n - 1:0];nodeS0[pNode] = (port0[0] == port1[0])? 1'b1 : 1'b0;} } *else if* (port1[n-1:1] < port0[n-1:1) {

```

pNode = port0[n-1:1];

if (port0[0]) {

nodeValue1[pNode] = port1[n - 1:0];

nodeS1[pNode] = (port0[0] == port1[0])? 1'b1 : 1'b0;

}

else {

nodeValue0[pNode]] = port1[n - 1:0];

nodeS0[pNode] = (port0[0] == port1[0])? 1'b1 : 1'b0;

3

}

```

else null;

Note that each port register has width of  $log_2^N$  bits with the top  $(log_2^N - 1)$  bits representing the output switching node number and the least significant bit representing the port number (0 or 1) of the output switching node as well as the parity of the output port index.

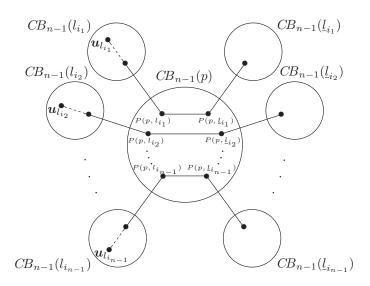

Fig. 6 Initialization

After the initialization step, all output switching nodes will be divided into one or more classes depending on the permutation of inputs/outputs as shown in Fig. 6. All nodes in the same class are bounded together such that once the state value of any node is determined, then the state values of all the other nodes will be determined. For the example shown above, if the switch setting value of b0 is 0, then the state values of the whole class are shown in Fig. 6.

### SEARCH

In the searching step, all processing elements parallelly search and update the node pointer till reaching the representative node of the class, i.e., the switching node with the smallest index number in the class. The number of searching steps is bounded by  $\frac{N}{2}$ . As shown in Fig. 5, right after the state machine runs into the SEARCH state, each processing element  $P_i$  updates nodeValue0/1[i] and relation values nodeS0/1[i] stored locally till the pointer's values do not change in the current searching iteration. To detect the ending condition of searching step, before searching in SEARCH state, the node pointer's current value nodeValue0/ 1 will be stored in *preNodeValue*0/1.

Fig. 7 shows that after searching all processing elements point to one endpoint except the one representing b7, which reaches two endpoints b1 (node[1]) and b0 (node[0]). In each class, there is only one representative node. In order to solve this problem, we must merge these two end nodes pointed by the same processing element, as shown in Fig. 7, this process will be done in the MERGE state.

The following two conditions need be satisfied before transferring to the MERGE state.

- After one searching step, the value contained in register preNodeValue doesn't change.

- The switching node has type value "nodeType == 2'b11", which means the switching node points to two endpoints.

Fig. 7 Searching and Merging

At each processing element  $P_i$ , the following code is used to determine if transiting to the MERGE state. *if* ((*preNodeValue0* == *nodeValue0*) and

(preNodeValue0 == nodeValue1))

if (nodeType[1:0] == 2'b11)

if (nodeValue0 == nodeValue1)

state = MERGE\_SN;

else state = MERGE;

else state = DONE;

else state = SEARCH

If the two pointers of the switching node point to the same endpoint, then FSM transits to MERGE\_SN state, in which one of two pointers of the switching node will be reset to its initial value; otherwise, the FSM transits to the MERGE state.

### MERGE

When the processing element reaches the endpoints in both directions and the two endpoints are different, the merging step will be conducted. As in the initialization step, the node pointer with larger node index is updated with smaller node index number. As shown in Fig. 7, the processing element merges the endpoints of b7 overwriting the nodeValue register storing b1 to b0. We can also see that, after the merging process, the switching nodes previously pointing to node b1 need be updated to pointing to b0. For the example in Fig. 7, after the merging step, nodes b6 and b4 need go through searching step again to update their pointers to the representative node b0.

For each processing element  $P_i$ , the following code is used to update pointers.

if (nodeValue0[i] < nodeValue1[i])

*if* (*nodeValue*1[*i*][0]) {

nodeValue1[nodeValue1[i]/2] = nodeValue0[i]; nodeS1[nodeValue1[i]/2] = nodeS0[i] XOR nodeS1[i]; } else {

nodeValue0[nodeValue1[i]/2] = nodeValue0[i];

nodeS0[nodeValue1[i]/2] = nodeS0[i] XOR nodeS1[i];

else if(nodeValue0[i] > nodeValue1[i]) {

if (nodeValue0[i][0]) {

nodeValue1[nodeValue0[i]/2] = nodeValue1[i];

nodeS1[nodeValue0[i]/2] = nodeS0[i] XOR nodeS1[i] }

else {

nodeValue0[nodeValue0[i]/2] = nodeValue1[i];

nodeS0[nodeValue0[i]/2] = nodeS0[i] XOR nodeS1[i];

}

}

else null;

After the merging step, the processing element will notify the other processing elements so that all the other processing elements will transit to the SEARCH state. As shown in Fig. 7, after the searching step, all the switching nodes point to the representative node of this class. The initial state value for the representative node 'b0' of this class is '0', then the state value of all other switching nodes can be determined by the relation value nodeS in parallel. And the switch state values shown in Fig. 7 is exactly the same as those values shown in Fig. 6.

In our design, after all processing elements are in DONE state the mainframe will set the state values of output and input switching nodes.

C. Setting State Values of Output Switching Nodes and Input Switching Nodes

The state values for output switching nodes  $outNodeStateValue\left[\frac{N}{2} - 1:0\right]$  can be obtained directly from the relation value  $nodeS0\left[\frac{N}{2} - 1:0\right]$  or  $nodeS1\left[\frac{N}{2} - 1:0\right]$  as

outNodeStateValue[j] = NodeS0[j] | NodeS1[j];.(8)

After the state values of output switching nodes are determined, the state values of input switching nodes are determined too. According to the symmetric routing constraint, the state value of an input switching node is equal to or opposite to the state value of its corresponding output switching node which depends on the relation of the input/output port index number.

Given permutation pair (k, l), where k is the input port number, and l is the output port number, due to the symmetric self-routing constraint, i.e., Eqn. (4) and (5), we have:

$$inNodeStateValue \left[\frac{k}{2}\right] = \begin{cases} outNodeStateValue \left[\frac{l}{2}\right] & \text{if } k, l \text{ are same parity} \\ \sim outNodeStateValue \left[\frac{l}{2}\right] & \text{if } k, l \text{ are opposite parity} \end{cases}$$

(9)

where k/2 and l/2 give the corresponding input/output switching node index. As we can see, either port[2i] or port[2i + 1] can be used to determine the relation between state values of input switching node and its corresponding output switching node. Here we use port[2i] to do the calculation. And port[2i][0] gives the parity of the output port.

// For i=0, 1, ..., N/2 if (port[2i][0])  $inNodeStateValue[i] = \sim outNodeStateValue\left[\frac{port[2i]}{2}\right];$

else

$inNodeStateValue[i] = outNodeStateValue\left[\frac{port[2i]}{2}\right];$

### IV. EXPERIMENT RESULTS

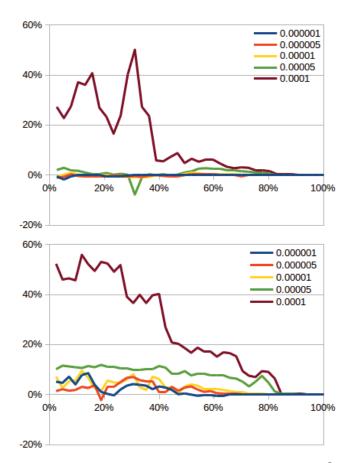

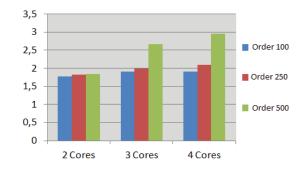

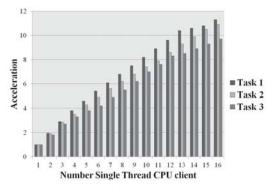

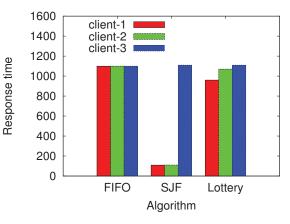

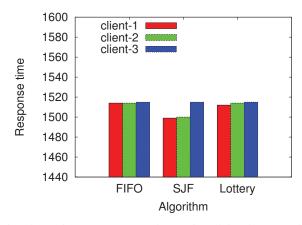

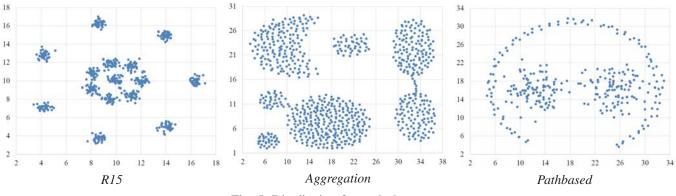

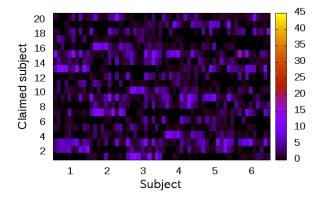

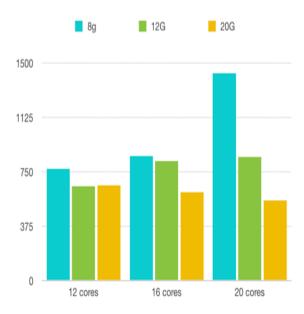

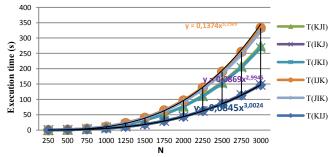

We have implemented the Lee's algorithm for finding the switch settings for input/output stages of 8x8 to 32x32 Benes networks in Verilog, simulated and synthesized the designs using Cadence tools. The RTL code is written in parameterized way so that it is easy to expand to larger sizes. In the simulation process, ModelSim is adopted as the simulation tool. For each design, five categories of permutations are used for validation including bit reversal, perfect shuttle, butterfly, matrix transpose, and random permutations. Under each category, one or more different permutations have been tested. In the synthesis process, Cadence Encounter RTL-Compiler is used with TSMC 65nm technology library. All size designs are synthesized under the same settings. The synthesized results are presented below

TABLE II. TIMING RESULT

| Benes Size                  | 8x8      | 16x16    | 32x32    |

|-----------------------------|----------|----------|----------|

| Critical Timing Delay (ps)  | 8.34E+02 | 2.30E+03 | 3.68E+03 |

| Time Complexity $O(log^2N)$ | 9        | 16       | 25       |

The timing delay is mainly decided by the time complexity of the algorithm. While the size of the processing element will not affect the timing delay as much as that does to area and power consumption. The complexity of algorithm is determined by the number of searching steps. The simulation results in Table II show that the number of searching steps follows O(logN).

TABLE III. CELL NUMBER AND AREA

| Benes Size      | 8x8      | 16x16    | 32x32    |

|-----------------|----------|----------|----------|

| Number of Cells | 1.81E+03 | 8.11E+03 | 3.62E+04 |

TABLE III. shows the area result in terms of number of cells, the basic design unit used to measure the logic complexity. When the network size is doubled, the number of cells increases by about 4 times. It is clear that in Lee's algorithm, when the network size is doubled, the number of processing elements needed in each stage is doubled. For example, the  $8 \times 8$  Benes has 4 processing elements and the  $16 \times 16$  Benes network has 8 processing elements. Besides, the logic complexity of the processing element nearly doubles when the network size is doubled. Overall, the logic complexity of the processing element should be increased by four times when the network size is doubled. This explains the trend of number of cells in TABLE III.

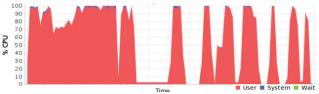

TABLE IV. POWER CONSUMPTION

| Size<br>Power Type | 8x8      | 16x16    | 32x32    |

|--------------------|----------|----------|----------|

| Leakage (nW)       | 9.24E+04 | 3.86E+05 | 1.76E+06 |

| Internal (nW)      | 8.46E+04 | 3.85E+05 | 1.69E+06 |

| Net (nW)       | 2.98E+04 | 1.42E+05 | 6.04E+05 |

|----------------|----------|----------|----------|

| Switching (nW) | 1.14E+05 | 5.28E+05 | 2.29E+06 |

TABLE IV. shows the power consumption of the design in terms of static (internal) power, dynamic (mainly switching), net and leakage power. Each portion of power increases significantly as the radix of Benes network increases. The power consumption increasing trend is consistent with the increasing trend of number of cells. The switching power is the most significant portion, followed by internal (static) and leakage power which occupies 36%, 28% and 27% of total power, respectively. Together the three portions of power dominate the power consumption at more than 90%.

#### V. CONCLUSION

This paper presents the RTL design of a parallel switch setting algorithm in Benes Networks. We have refined the algorithm in data structure and initialization/updating of relation values to make it suitable for hardware implementation. The simulation and synthesis results confirm that the timing, area, and power consumption of the circuit is consistent with the complexity of the Lee's algorithm.

#### REFERENCES

- K. N. Levitt, M. W. Green and J. Goldberg "A study of the data commutation problems in a self-repairable mutiprocessor." in *Proc. Spring Joint Computer Conf.*, 1968.

- [2] Y. Kao, M. Yang, N. S. Artan, and H. J. Chao "CNoC: high-radix Clos network-on-chip," in *IEEE Trans. Computer-Aided Design of Intergrated Circuits and Systems*, vol. 30, no. 12, pp. 1897-1910, Dec. 2011.

- [3] H. Liu, L. Xie, J. Liu, and L. Ding, "Application of butterfly Closnetwork in network-on-chip," *The Scientific World Journal*, vol. 2014, pp. 1-11, 2014.

- [4] A. Joshi, C. Batten, Y. Kwon, S. Beamer, I. Shamim, K. Asanovic, V. Stojanovic, "Silicon-photonic Clos networks for global on-chip communication," in *Proc. 3rd ACM/IEEE Int'l Symp. Networks-on-Chip* (*NoCS*), 2009, pp. 124-133.

- [5] T. T. Lee and S. Y. Liew, "Parallel routing algorithms in Benes-Clos networks," in *Proc. 15th INFOCOM*, 1996 vol.1, pp.279-286.

- [6] Y. Kai, K. Hamada, Y. Miao and H. Obara., "Design of partiallyasynchronous parallel processing elements for setting up Benes networks in O(log2N) time," in *Proc. Int'l Conf. Photonics in Switching*, 2009, pp. 1-2.

- [7] Y. Yeh and T. Feng, "On a class of rearrangeable networks" in *IEEE Trans. Comput.*, vol. 41, no. 11, pp. 1361-1397, Nov. 1992.

- [8] A. Waksman, "A permutation network," J. Ass. Comput. Mach., vol. 15, pp. 159-163, Jan. 1968.

- [9] D. Nassimi and S. Sahni, "Parallel algorithms to set up the Benes permuation network", *IEEE Trans. Computer*, vol. c-31, no. 2, pp. 148-154, Feb. 1982.

- [10] K. N. Levitt, M. W. Green, and J. Goldberg, "A study of the data commutation problems in a self-repairable multiprocessor", in *Proc. Spring Joint Computer Conf.*, 1968, vol. 32, pp. 515-527.

- [11] T. T. Lee, S. Y. Liew, "Parallel routing algorithms in Benes-Clos networks", *IEEE Trans. Commun.*, vol. 50, no. 11, pp. 1841-1847, Nov. 2002.

- [12] H. Richter, "Real-time interconnection network for single-chip manycore computers," in *East-West Design & Test Symp.*, 2013, pp.1-4.

- [13] H. Moussa, O. Muller, A. Baghdadi, M. Jezequel, "Butterfly and Benesbased on-chip communication networks for multiprocessor turbo decoding," in *Proc. DATE*, 2007, pp.1-6.

- [14] H. S. Stone, "Parallel processing with the perfect shuffle," *IEEE Trans. Comput.*, vol. C-20, pp. 153-161, Feb. 1971.

# Traceability Acquisition Method for Network Security using Multiple Encryption and Decryption of the Tag in Packet

Kento Masukawa, Kenichi Takagiwa, Tadanori Matsui, Hiroaki Nishi Graduate School of Science and Technology, Keio University, Japan <sup>+</sup>{masukawa, takagiwa, matz, west}@west.sd.keio.ac.jp Pagular Pasearch Paper

Regular Research Paper

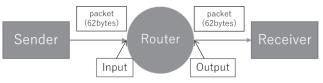

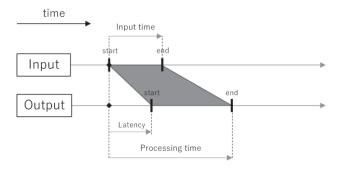

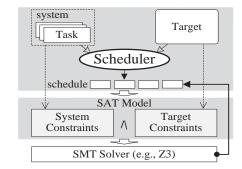

Abstract – Multi-factor authentication is used to improves the existing vulnerability of traditional password authentication, such as biometric and onetime password token. However, these methods foist a burden on the user. We propose the traceability acquisition method in a network for the user authentication, which runs only on the routers; thereby it achieves secure and authenticated communication between a user and a server application without any burden on the users and applications. In this method, "tracer tags" is introduced for attaining packet traceability of a packet and the tags are encrypted with unique router's key. Recipient makes sure that packet has delivered through the expected routing path by decrypting a tracer tag. The Proposed method achieved secure and authorized communication using packet traceability without any additional effort to users The proposed method is evaluated in a virtual environment. By using the proposed method, routing throughput decreased only by 3% compared with normal routing.

**Keywords:** network security, routing information, multi-factor authentication, multiple encryptions, tag information.

# **1** Introduction

The combination of username and text password is the most common authentic method as the user authentication of a Web service. The text password authentication should choose a strong password to resist brute-force or dictionary attack [1]. However, a strong password which combines multiple random alphabets, numeric and special characters are difficult to memorize for a human being. Many users are using the easy-to-remember weak passwords. Reusing the password across multiple Website also promotes the vulnerability of text password authentication [2]. Florencio and Herley indicated that user reuses the same password across 3.9 Web services on average [3]. Reuse of password could expand the damage to multiple Web service caused by password leak from one of Web services. This attack is called Password Reuse Attack.

In addition, Password Stealing Attacks (PSA) must be taken into consideration. The phishing site is the most common as a method of PSA. According to the APWG report [4], the total number of phishing attacks was observed in the 4<sup>th</sup> season of 2016 was a review 158,574.The email address has been used for user identification in many Websites. Therefore, password theft leads to crack user accounts.

Some researchers focus on multi-factor authentication to provide more reliable user authentication. NIST announced SP800-63-2 [5] for guidelines of online authentication; there are the following three factors.

- SYK(Something You Know)

- SYH(Something You Have)

- SYA(Something You are)

Text password authentication is categorized in the SYK. One-time password token is SYH. Biometric authentication is SYA. Multi-factor authentication utilizes the SYH or SYA beside the password. Although these multi-factor authentications improve security by convoluted user authentication, it incurs expensive to introduce compared with password authentication [6]. These methods also need new processes to the users such as preregistering biometric information and creating a one-time password, and burden on users is increased. Therefore, people who are not aware of security do not use multifactor authentication. For protecting private information, there is a need for a method to improve security using multifactor authentication without increasing the user burden.

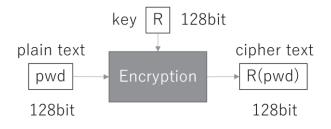

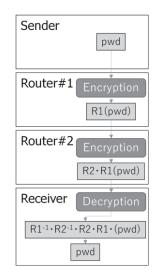

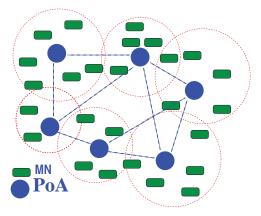

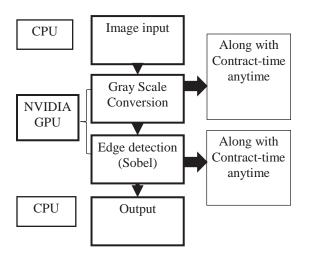

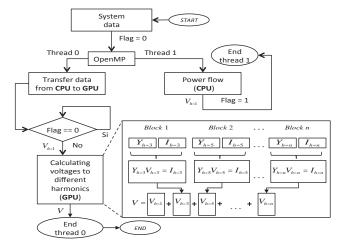

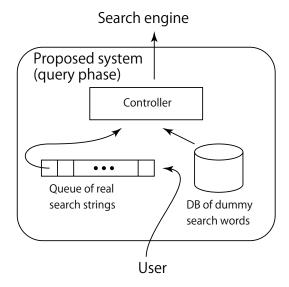

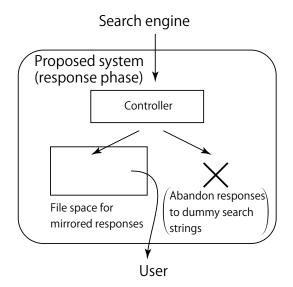

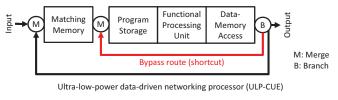

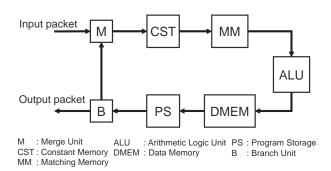

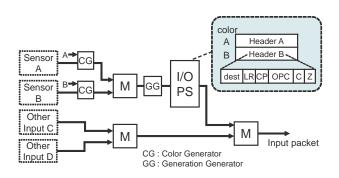

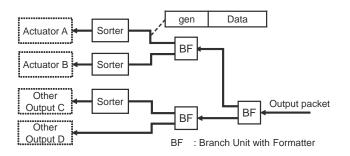

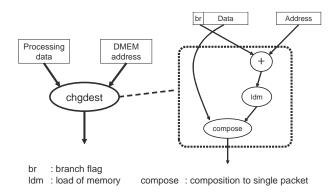

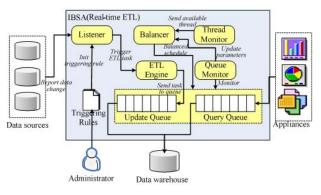

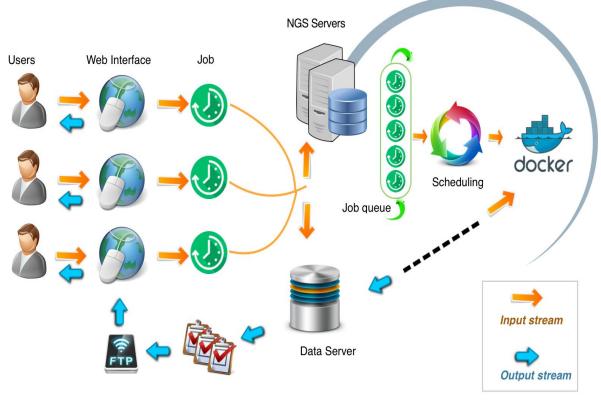

In this paper, we propose the traceability acquisition method in a network and apply it to the multifactor authentication, which requires no additional action to users. The tracer tag is stored in the packet, which is encrypted with each router during packet forwarding. The server acquires a traceability by analyzing the tag. This method requires special router which can analyze traffic and modify packet on the fly. Sevice-oriented Router(SoR) [7], a router is capable of analysis and processing of the packet, is used for this research. SoR is used for storing and encrypting tags in the packet.