# **SESSION**

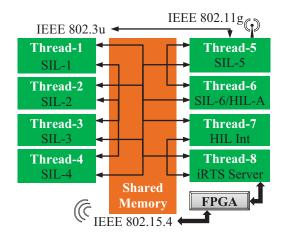

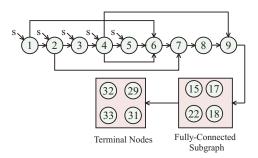

# CYBER-PHYSICAL SYSTEMS AND APPLICATIONS

Chair(s)

TBA

# Detection of Human Limits in Hazardous Environments: A Human-Centric Cyber-Physical System

Constantin Scheuermann<sup>1</sup>, Raman Tandon<sup>2</sup>, Bernd Bruegge<sup>1</sup> and Stephan Verclas<sup>3</sup>

<sup>1</sup>Department of Computer Science, Technical University Munich, Munich, Germany <sup>2</sup>Wehrwissenschaftliches Institut fuer Werk- und Betriebsstoffe, Erding, Germany <sup>3</sup>T-Systems International GmbH, Munich, Germany

Abstract—Harsh and hazardous working conditions can push humans to their limits when completing their tasks. Smart Textiles, wearables and 3D printing technology enable us to form Human-Centric Cyber-Physical Systems (HC-CPSs) that put the human in the center of the system design. HCCPSs aim to increase operational safety by monitoring for example health parameters and providing support to humans. Wrong or even not present human risk management, the presence of physiological stress and human information overload can have dramatic consequences in harsh and hazardous working environments. Thus, unclear User Interface design, unpractical monitoring techniques as well as complicated communication channels can impede human support. We brought together researchers from different domains and collaborated with the startup (ambiotex) to form the vertical prototype Cooling Health Safety Textile (CHEST). CHEST is a browser based remote health monitoring system using easy applicable smart textiles and a lean communication channel together with an app based visualization software. We offer a lean User Interface to minimize information overload and physiological stress. Currently, we are working on the integration of a smart cooling system integrated into the worker's textile.

**Keywords:** Physiological Stress, Health Monitoring, Human-Centric Cyber-Physical Systems, MQTT, Smart Textiles, Wearables

# 1. Introduction

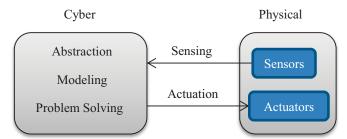

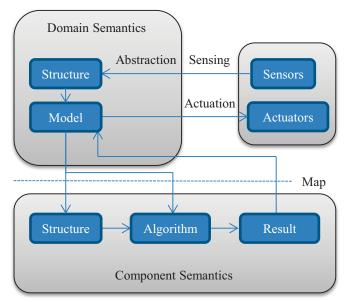

Technical improvements over the last 70 years are enabling researchers and industries to build Human-Centric Cyber-Physical Systems (HCCPSs). Especially the miniaturization of sensors, actuators and computer chips made it possible to generate "wearable" IT-devices. HCCPSs are bridging the cyber and IT environment and the physical environment that includes human beings. HCCPSs put the human into the center of the system design. Combining technologies such as tiny, energy-efficient mobile devices with applicable sensors and actuators is a requirement to integrate smart systems seamless into daily objects. The use of smart textiles in combination with wearables allows us to focus on humans and reconceive as well as extend existing concepts and processes. HCCPS consider humans as part of the system. The human condition as well as human behavior serve as system input. Such input can be error prone. Feedback and communication channels are essential to allow quasi real-time system state monitoring, especially for HCCPSs.

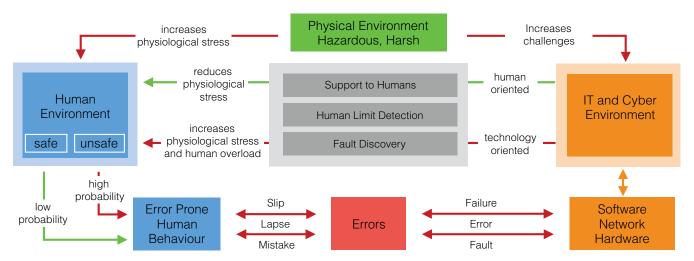

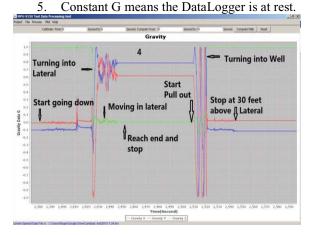

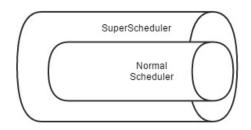

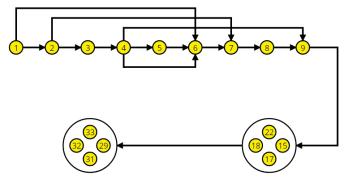

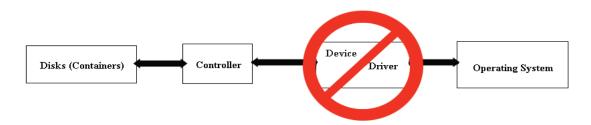

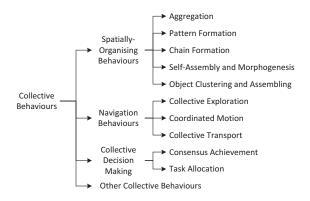

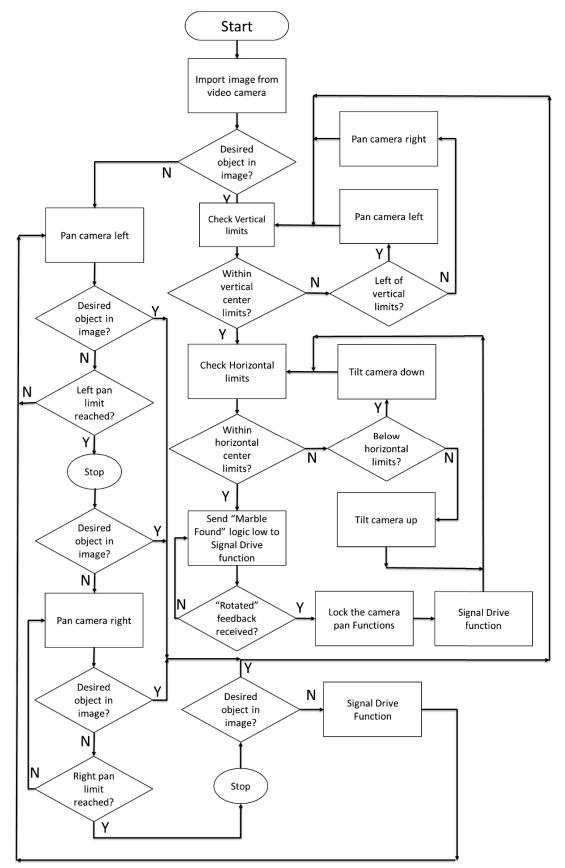

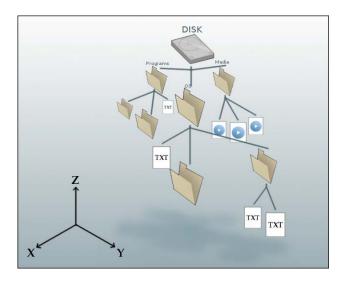

Within HCCPSs erroneous behavior and its results are a major issue to address. Such erroneous behavior can lead to operational safety risks. Fig. 1 shows the influence factors that can increase or decrease the probability of errors to happen. Erroneous behavior can be found in different layers within a HCCPS, either in the human environment or in the cyber and IT environment (Software, Network and Hardware). Within HCCPSs the human is the center of the system design and the cyber and IT environment needs to be human orientated in order to reduce human based errors. As one might know from every day life, the more things we do in parallel the more stress we feel. The same applies for information overload while using IT systems. The caused physiological stress can create human induced errors. Especially, in harsh working environments, stress, great responsibility, dependencies and the risk of lives are prominent challenges for humans. Errors in such environments need to be reduced or even avoided using a system that tries to reduce or eliminate physiological stress factors.

According to James Reason, human errors can be categorized as *Mistakes*, *Lapses* and *Slips*. *Mistakes* refers to an incorrect plan while identifying a goal and selecting the tools to achieve the goal. *Lapses* occur in case the chosen plan, to achieve a certain goal, is postponed, and needs to be stored. In case the plan needs to be memorized and thus a longer time period passes, errors can occur. *Slips* are errors that appear during an action [1]. Sanders and McCormick define human error as "an inappropriate or undesirable human decision or behavior that reduces, or has the potential of reducing effectiveness, safety, or system performance" [3]. In literature, human errors are also referred to as humanmade faults caused by human actions or the absence of human action. They have phenomenological causes as well as physical hardware faults. [4].

Physical Hardware faults are natural faults caused by natural phenomena without human participation. Software faults such as software bugs are widely addressed in the research field of software engineering. Concepts as continuous integration or test driven development try to keep such errors

Fig. 1: Focus of HCCPSs: Human-Centric Cyber-Physical Systems have to deal with high complexity due to the included subsystems. Human behavior is error prone as humans are doing mistakes, lapses and slips [1]. The Software, Network and Hardware subsystems can contain faults that result in errors and in the worst case cause failure. As the human is the center of the system, information overload and physiological stress can be the result. HCCPSs try to decrease these factors by offering Support to Humans, Detection of Human Limits and Fault Discovery. Human oriented design can decrease physiological stress while technology oriented design can increase information overload and physiological stress. The Illustration is based on [1] [2] and extended.

(bugs) at a minimum. Radio signal jamming, signal hijacking and physical phenomena such as fading and pathloss can for example cause network faults. [4] [5]

As shown in Fig. 1 the error complexity covers 3 layers: Human environment, Physical Environment and the IT and Cyber environment. We state that HCCPSs cannot be error free and are highly error prone due to the complexity of potential error sources. As humans are the center of the system design, Support to Humans, Human Limit Detection and Fault Discovery are aspects we want to address. We suggest deploying real-time human observers, which can monitor the system concerning all three error layers.

Humans are still an important part of professional work routines and processes in industries. In professional hazardous environments they work in tight cooperation with robots. Yet for scenarios where robots cannot access or the environment is just not suitable for a robot, humans have to operate. In this study we focus on risk minimization for the workers wearing CBRN-protective suits through permanent monitoring of the vital signs utilizing a smart textile. Since these CBRN-suits are totally impermeable the worker is exposed to dramatic heat stress and thus can easily collapse. Therefore, medical staff monitors via wireless live data transmission the vital signs of the worker wearing a CBRN-suit. The Ebola virus disease or the Fukushima catastrophe, are typical scenarios where humans have to operate in harsh environments, wearing CBRN-suits. Currently, real-time remote health monitoring, including a feedback channel between the worker, a medcial advisor (MC) and

a commander, during such missions is difficult to achieve<sup>1</sup>. Current monitoring systems allow only an analysis of data after the mission has ended and real-time monitoring is yet in its infancy. Additionally, we investigate on a Human Limit Detection system offering real-time observer monitoring capabilities.

Self monitoring capabilities as well as health stress level dependent cooling capabilities should contribute to a better wearing comfort of CBRN suits, decrease physiological stress of the worker and result in longer working times than now. Currently, humans wearing such suits are only allowed to operate 30 minutes<sup>2</sup>. We propose smart cooling systems considering the health condition of the humans wearing CBNR suits. The paper is structured as follows: Section 2 describes the related work. Section 3 explains the problem we want to address followed by Section 4 which explains the Visionary Scenario. In Section 5 we describe the system design and then conclude with Section 6 and 7.

# 2. Related Work

We state that human health monitoring is the prerequisite to allow operational safety in professional harsh working environments. With the invention of the stethoscope by Rene Laennec in 1816, a first step towards health monitoring was done. Further inventions improved the first stethoscope such

<sup>&</sup>lt;sup>1</sup>Personal Discussions with Dr. Raman Tandon and his collegues

<sup>&</sup>lt;sup>2</sup>DGUV (Deutsche gesetzliche Unfallversicherung) http: //publikationen.dguv.de/dguv/pdf/10002/r-189.pdf and http://publikationen.dguv.de/dguv/pdf/10002/ r-190.pdf

as the ECG with the contribution of Willem Einthoven. With the invention of the Holter-Monitor, an electrocardiography device that can monitor the activities of the cardiovascular system, the first continuous health monitoring was possible. In sports, heart rate monitors became popular since the 1990s [6]. Nowadays, a variety of devices are commercially available and monitoring systems are even integrated into smart textiles<sup>3</sup>.

During the last decades, health-monitoring is an emerging field in research. Research efforts cover structural [7] as well as human health monitoring applications. An extensive overview of existing applications especially concerning patient health monitoring can be found at [8].

Generally, health monitoring systems can be wire-based or wireless. Wire-based systems have major disadvantages such as being tethered to one location, they typically support a short observation period and cannot be placed to real environments [9]. The major advantage is that wire-based systems profit from a reliable data connection. Still considering scenarios where the patient is mobile, cable connections can be a major impediment. To improve user's comfort the usage of conductive yarns, woven into a textile form conductive textiles: so called 'Smart Textiles'. Wireless systems have to face typical challenges such as power consumption, and limited energy resources, security, fading and pathloss, signal jamming as well as limited bandwidth. The major advantage is the location independent operation capability.

Concerning human health monitoring several terms are currently present in research. (Wireless) Body (Area/Sensor) Networks, Wireless Medical Telemetry Services, Wireless physiological measurement systems, Wearable Wireless Health-Monitoring System (WWHMS).

(Wireless) Body (Area/Sensor) Networks have their origin in the medical and health domain. The terms first appeared in literature in the early 21st century. Such systems focus on the aging population to address common chronic age related diseases. Typical representatives of these diseases are congestive heart failure, chronic obstructive pulmonary disease, arthritis, osteoporosis, and dementia [9] [10]. Typical challenges are scalability, security and privacy [10]. To realize Wireless Medical Telemetry Services the Federal Communication Commission (FCC) allocated the WMTS spectrum that is used for remote patient health monitoring applications. Wireless medical telemetry systems include devices to measure patients' vital signs and other important health parameters (e.g., pulse and respiration rates).<sup>4</sup>

Wireless physiological measurement systems (WPMS) make use of wireless transmission capabilities. WPMSs allow

<sup>4</sup>https://www.fcc.gov/general/

Active

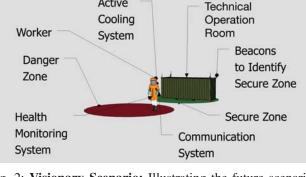

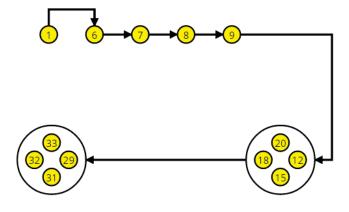

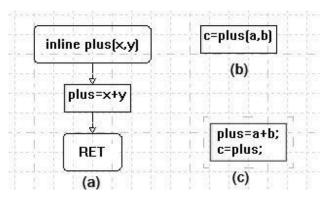

Fig. 2: Visionary Scenario: Illustrating the future scenario divided into the secure and danger zone. The worker is equipped with an active cooling system, a communication system and a health monitoring system. The secure zone provides the independent communication infrastructure and an identification technology to mark the secure zone.

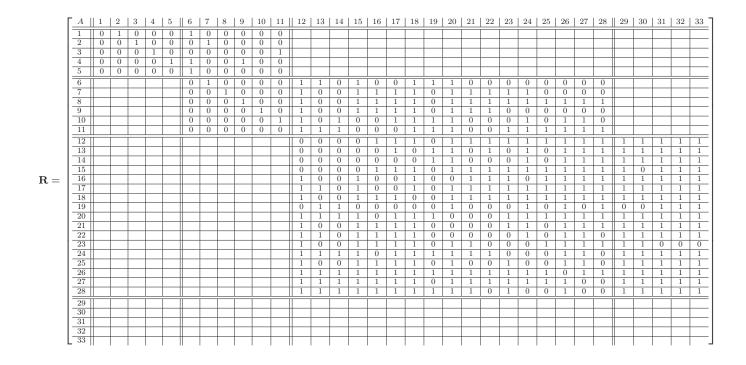

real-time physiological data measurements originated from wearable/implantable medical sensors. Data is collected and transmitted to a central processing unit. The primary purpose of the WPMS is to improve the quality and efficiency of healthcare (GE Healthcare 2007).

Wearable Wireless Health-Monitoring Systems (WWHMS) track the individual's activities continuously, transmitting the relevant information back to medical professionals. WWHMSs automatically alert health-care personnel when an emergency occurs. The major goal is to prevent delays of emergency medical services in the event of accidents. Delays can often result in serious physical and psychological consequences, permanent disabilities, or even fatalities. [10]

Several standards exist that are commonly used for the above-mentioned health monitoring systems: IEEE 802.15.6, ZigBee, Bluetooth, Bluetooth low energy, Infrared, UWB, Sensium and ANT. The standards mainly focus on the constrain resources such systems have to cope with: power efficiency, energy scavenging or power harvesting, robust communication and high throughput. Other challenges are the form factor, operational safety and security, clinical effectiveness of sensor technology, artificial intelligence and decision support as well as security [10].

As we are combining real-time human condition monitoring, remote monitoring and smart textile cooling concepts, some related work in these research areas is provided. Projects such as the LifeGuard [11] system can monitor two standard electrocardiogram leads, respiration rate via impedance plethysmography, heart rate, hemoglobin oxygen saturation, ambient or body temperature, three axes of acceleration, and blood pressure. Real-time health monitoring in harsh environments is essential for the worker in order to ensure a safe working environment.

Autonomous water and gas based cooling systems already

<sup>&</sup>lt;sup>3</sup>Ambiotex Shirt, Zephyr Bioharness, Vivonetics Life Shirt, Hexoskin, Athos Muscleshirt, Health-Lab

wireless-medical-telemetry-service-wmts Allocated frequency band by FCC for Wireless Medical Telemetry Services (WMTS) in the 608-614, 1395-1400, and 1427-1432 MHz range.

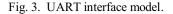

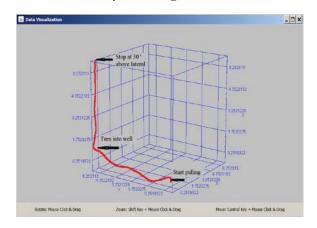

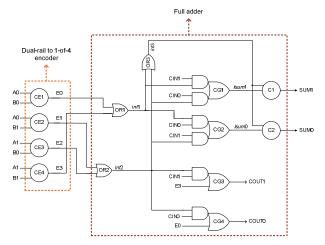

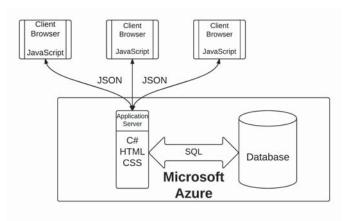

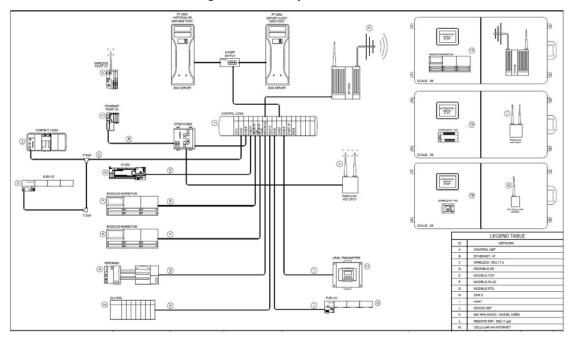

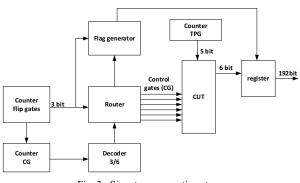

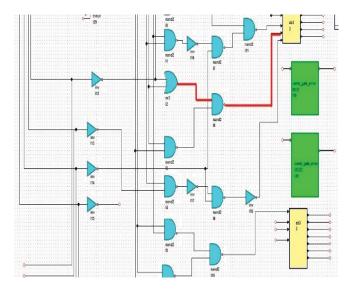

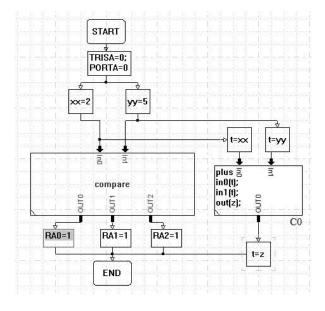

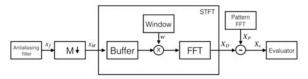

Fig. 3: Component Diagram: Showing the provided and used services of each subsystem.

exist such as the combo cool system<sup>5</sup>. Also heated undergarment<sup>6</sup>, as well as socks and insoles and gloves<sup>7</sup> are already commercially available.

Latest advances within 3D printing technologies and 3D weaving technologies<sup>8</sup> allow us to integrate and print cooling structures directly as textiles-based structures.

The combination of remote health monitoring systems, smart textiles and intelligent cooling systems enables us to develop a Human-Centric Cyber-Physical System, putting the human and his condition into the center of the system design. We want to transfer the knowledge from WWHMS to professional applications in harsh, hazardous environments. In our definition harsh environments require special kind of heavy-duty equipment such as CBRN-suits that are totally sealed off from the environment. In this case, cooling is of major concern as workers in such suits face the danger of collapsing and suffer from severe thermal stress.

# 3. Problem

Humans perform tasks in several areas. Tasks cover exhausting physical and mental work. Especially during physically exhausting tasks, humans can benefit from information

<sup>7</sup>Alpenheat, WarmX, Therm-ic, Reusch, Interactive Wear

about their health condition. For a professional football player the information about his heart rate can provide a major benefit, as the player should meet a certain training target heart rate. For a professional fire fighter, knowledge about the health condition can improve operational safety during a mission. A collapse, as the most drastic consequence while performing a task in hash environments, needs to be avoided. It can not only influence the operational safety of the fire fighter, but moreover it can influence the entire mission outcome including the involved team members.

To monitor the health condition, several applications are already available for consumers as well as for professionals. For professional athletes such applications help to monitor, control and optimize their performance and training schedule. For professionals operating in harsh environments such monitoring systems can be used to realize remote health monitoring in combination with smart cooling capabilities. Especially in hazardous environments, where CBRN-suits are a requirement, the danger of collapse resulting in a human error is a proper risk.

If we are imagining a worker operating in an environment that is contaminated, the isolation of his working suit is a requirement to guarantee operational safety. As the suit is totally isolated, air exchange with the environment is up to impossible. Due to the lack of air exchange several consequences appear. In addition to high environmental temperatures the muscles of the worker produce heat during the operation. This heat increases the temperature within the suit to a level where the worker starts to perspirate. In case we assume a normal workload of 120 Watt a worker operating in a CBRN-Suit evaporates/perspirates up to 0.5 1 of sweat in one hour that currently accumulates inside the suit. The sweat accumulates at the tip of the limbs and parts such as the back, head and the chest. The humidity causes swollen, soft finger and toe tips that can cause injuries or can impede a proper task completion. As a result of the thermal stress the heart-rate and blood pressure increase making a collapse more likely. An experiment conducted by Glitz et. al. showed that taking a break would stop muscle heat production but has no significant effect on the thermoregulation of the wearer, since the CBRN-suit is impermeable. For the experiment 10 participants were wearing protective overalls and completed a 130 minutes work-rest schedule in non-ventilated (non-vent.) and ventilated (vent.) thermal insulating protective clothing. It was shown while wearing the ventilated suit the heart rate during the stops almost dropped to normal (90 b/min) whereas in the non-vent. situation the participants' heartrate steadily increased up to 150 b/min and only dropped to 135 b/min during the last break [12]. For professionals, operating in harsh environments, physical overstrain can result in the risk of life for each member of the task force and even for the entire team. Currently, such workers are not allowed to operate more than 30 minutes. This period of time is

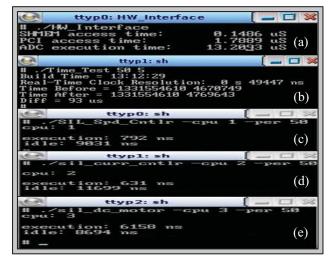

<subsystem>> Apple Watch Extension <<subsystem>> Monitoring Server component>

Mission Data Fetch& Save Data O <component>> ţ <subsystem iOS App ŝ Push Registration Data <<component>> Data Manager <<subsystem>> Message Server Health Data Publish8 <<component>> Sensor Handler MQTT Broker Push Historical Health Data Registration& Mission Data ŝ <component>> Mission Controll <component>> Bee-Wi <subsystem>> <<subsystem>> Monitoring Frontend

<sup>&</sup>lt;sup>5</sup>http://wolfengineering.de/personen-kuehlung

<sup>&</sup>lt;sup>6</sup>http://voltheat.com/, Alpenheat, WarmX, Therm-ic, Reusch, Interactive Wear.

<sup>&</sup>lt;sup>8</sup>3D Weaver http://www.sosafresh.com/3d-weaver/

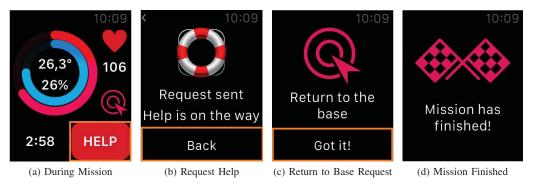

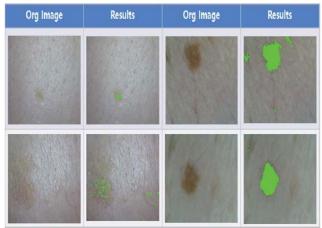

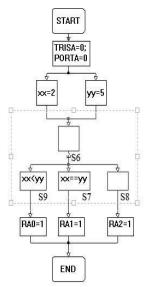

Fig. 4: **Smart Watch Application:** shows the main Watch UI screens. During the mission the worker can view different quantities such as humidity, temperature inside the suit, the heart rate and the elapsed time. The participant can ask for help using the help button. Request help shows the screen when the worker requested help. Return to Base shows the UI as soon as the Commander requested a return. As soon as the worker returned to the secure zone the mission finished screen is shown. All buttons are highlighted with an orange border.

in most cases not sufficient to complete a task. In order to extend that working period the deployment of smart textiles in combination with mobile monitoring and cooling possibilities offers a solution (compare Fig. 3).

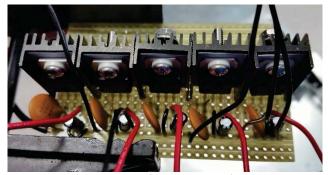

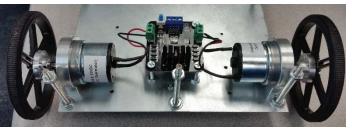

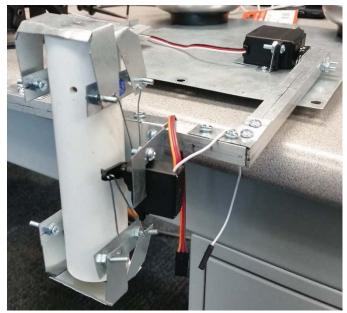

Currently, monitoring systems are hard-wired systems using sensors connected to a base unit in a shoulder bag. They can measure body temperature, the humidity in the suit and the heart-rate of the worker. An expert, the medical advisor, attaches the sensors to the worker. Each sensor is currently taped to the appropriate area on the body of the worker. During the mission a real-time monitoring is not possible as data-loggers are used. The doctor totally relies on his experience estimating the condition of the worker. The commander is the decision maker, deciding when a worker has to end a task. Consulting the doctor is inevitable for him. To the best of our knowledge, a comprehensive system that combines real-time monitoring, feedback channels between all stakeholders as well as context/condition dependent cooling is not available for heavy duty operations. The described system is our first vertical prototype showing the feasibility of the system design focusing on the software architecture. We conducted first experiments using 3D printing techniques in combination with smart textiles. We transferred knowledge from the domain of health monitoring to realize CHEST for heavy duty, harsh environment applications.

# 4. Visionary Scenario

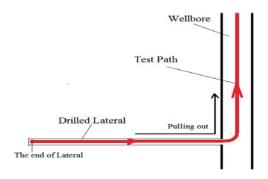

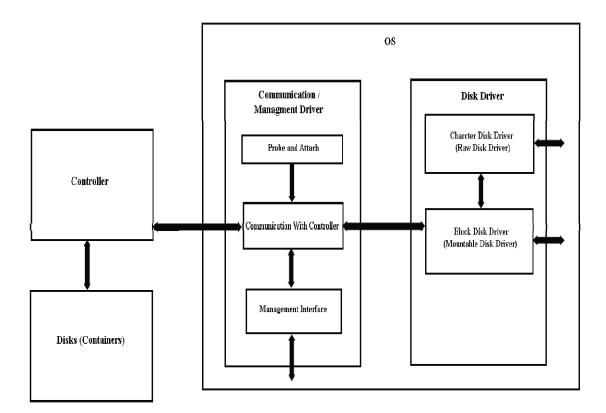

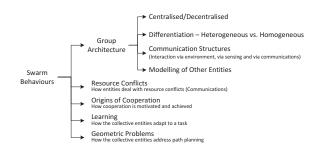

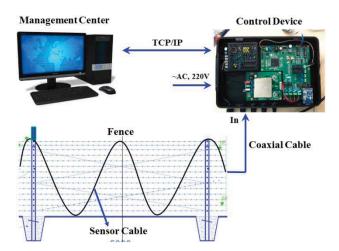

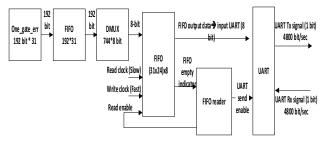

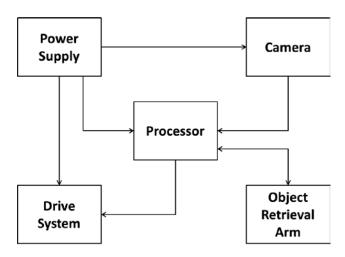

CHEST focuses on professional, harsh environments where workers are forced to use CBRN-Suits. Fig. 2 illustrates the visionary scenario during a contamination mission. Within the scenario, 3 actor roles are defined. The **Worker**, the **Medical Advisor (MA)** and the **Commander**. The worker receives instructions by the mission commander to fulfill the mission tasks. The MA is remotely monitoring the worker. All three actors are able to communicate with each other using an applicable communication system.

The environment where the scenario takes place is divided into two zones: the *secure zone* and the *danger zone*. The *secure zone* is the home base of the mission and is defined as safe environment. The base station is located within this zone. It consists of a container equipped with a wireless identification technology, that forms a geofence or halo around this area. Within the container all the infrastructure and equipment that is needed to monitor, control and communicate is located. Within the *danger zone* the worker has to operate. It is a harsh, hazardous environment, where special clothing such as CBRN-Suits are necessary.

Before the mission starts, the Workers are heading to the Commander. The Commander selects the Workers needed for the task, coordinates and plans the mission. As soon as the Commander has selected all the Workers needed for the mission, each Worker has to pick a CBRN-Suit from the stock. Each Worker is equipped with a personalized mobile device that is able to scan an identifier on each CBRN-Suit. After the identifier has been scanned the suit is mapped to the Worker who scanned it. As soon as the Worker is ready the mobile device is used to send the status to the Commander. The Commander receives a message in a browser application, which MA is ready to perform the task and arrange the group accordingly. An avatar represents each Worker. Additionally, a color-coded border indicating the technical integrity of the equipment surrounds each avatar. The Commander starts the mission and selects a MA, that is responsible for the health condition of each worker.

The **MA** in a separate part of the container can instantly see an anonymized view of all selected workers within the mission. The **MA** has no information about the CBRNsuit-worker mapping. Due to legal constraints the **MA** must not know about the identity of the **Workers** and must not receive any information that allows a person-data mapping. The Workers are now ready to start the mission. They are heading to the danger zone, operating and working on their task. The MA is able to monitor each participant and the system aggregates an overall status (stresslevel). In case a situation appears where a MA is entering a critical health situation, the MA can inform the Commander. The Commander receives a notification within the browser application. The Commander now decides if the Worker has to leave the *danger zone*. In case a Worker needs to leave the corresponding Worker should receive a notification on his wearable wrist device. Such a notification can be a vibration of the wearable device or an acoustic signal. As soon as the Worker returns to the secure zone, the CBRN-Suit can detect the halo of the secure zone and the Commander can see in his browser app that the corresponding Worker has arrived in the secure zone. In the following paragraphs we describe concrete visionary scenarios.

**Decontamination of Vehicles - Monitor and Control:** We assume that a worker needs to decontaminate several vehicles. Approximately, the task will take up to 1.5 hours. The MA that monitors the medical status of each worker needs to guarantee that the worker is still capable of working without risking health and therefore the safety of the worker. The MA needs to have a live monitoring system that is able to monitor how the workers' physical condition is. Therefore, the MA can monitor all data and even control the CBRN-suit remotely, namely airflow, heartrate and temperature. These are values that need to be controlled in quasi real-time if a dangerous situation occurs.

**Group Safety:** A group of workers are operating in a harsh environment within the danger zone. It is of major importance that each member during a mission knows about a potential risky situation of other group members. Therefore, each CBRN-Suit transmits critical conditions to the group members and to a monitoring system. In case of a potential collapse of a group member, everybody needs to know about this potential safety risk. They might help or support the other team member.

Web Based Consulting of Medical Advisors: In case of a potentially dangerous or critical situation the medical doctor might want to consult other medical advisors. The system should be able to create a shareable view of the current participant that other doctors can estimate if they come to the same conclusion.

**Documentation:** After a mission has finished all commands, actions and all data are stored for documentation reasons. As soon as they are stored, stakeholders from the administrative layer can be informed.

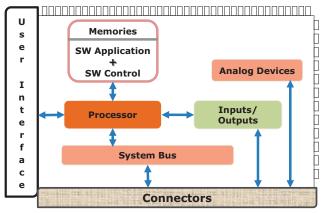

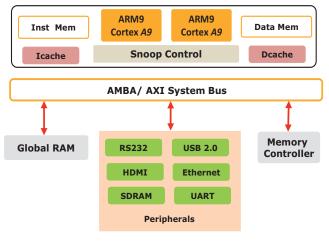

# 5. Subsystem Decomposition

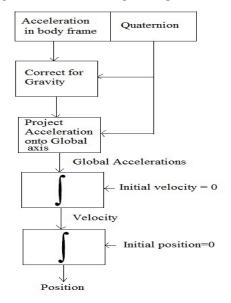

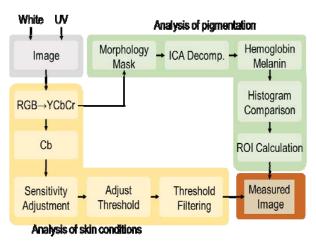

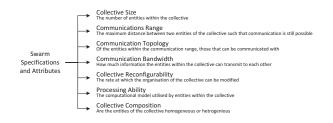

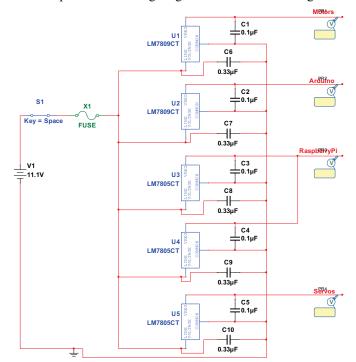

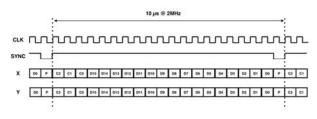

The communication between all subsystems is realized using a publish/subscribe mechanism in combination with RESTful services. The architecture includes a MQTT Broker architecture that CHEST is relying on. CHEST is decomposed into five subsystems, the Health Monitoring, the Smartphone, Smartwatch, the Monitoring Server and the Browser application.

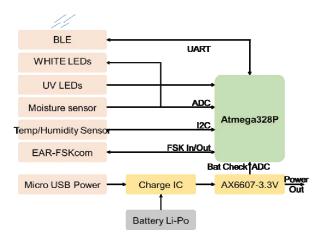

The Health Monitoring System can be further subdivided into the *Smart Textile* and the *Suit Sensors*. The *Smart Textile* is capable to monitor the heart rate and the Heart Rate Variability (HRV) as accepted indicator to monitor health condition [13]. The *Smart Textile* integrates the ECG sensors and a techunit that is collecting the vital data. It provides the data via Bluetooth low energy (BLE). In this prototype we used the ambiotex<sup>9</sup> shirt and cooperated with the manufacturer. The *Suit Sensors* are able to monitor the interior physical quantities such as temperature and humidity. We used a BeeWi<sup>10</sup> Weather Station as a first start. It also provides all measured data via BLE.

The *Smartphone* application is collecting the data from the *Health Monitoring* subsystem via BLE. It is capable of registering the worker and serves as center peace of data aggregation and communication. As communication channel we use WiFi at 2,4 GHz. Moreover, the subsystem can sense nearby BLE beacons that are used to detect the secure zone. It provides information for the *Smartwatch*.

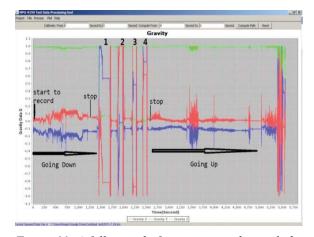

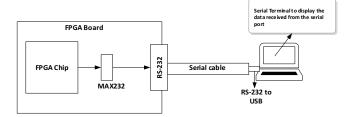

The *Smartwatch* serves as information display. It is able to provide vital data and instructions triggered by the MA or the Commander. It provides acoustic and vibration feedback to the worker. In Figure 4d the screens for the vital information, the help request, the command to return to the base and the mission finished screen is shown.

The *Monitoring Server* subscribes to special topics at the MQTT Broker. The topic structure is based on the roles described in Section 4. To estimate technical integrity the *Smartphone* provides a heartbeat mechanism to indicate the technical integrity of the system. The *Monitoring Server* stores all data during a mission. It provides a RESTful API to access historical data and specific time interval based data. Following the publish/subscribe mechanism a remote quasi real-time monitoring is possible.

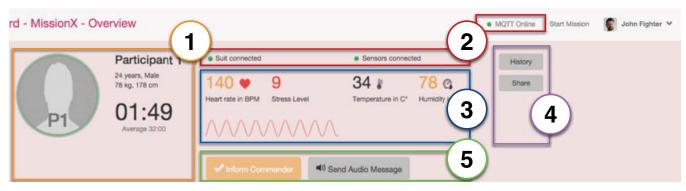

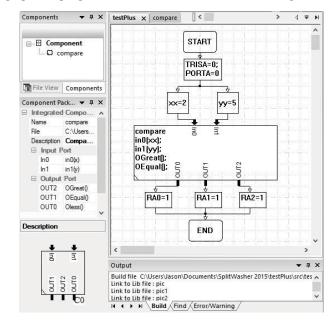

The Browser provides a User Interface for the MA and the Commander. It provides all relevant data in a dashboard kind of UI Design. Figure 5 shows the MA Dashboard. In the highlighted section (1) anonymized information about the participant can be seen. At (2) color coded indicators of the technical parameters can be seen. The MQTT Connection, the CBRN-Suit connection as well as the sensor connection can be checked. At (3) All measured values such as the heartrate variance can be monitored. The stresslevel can serve as an overall indicator about the current situation of the worker. In (4) historical data and sharing possibility controls are provided. Also Feedback possibilities are provided as

<sup>9</sup>Ambiotex www.ambiotex.com <sup>10</sup>BeeWi Weather Station

Fig. 5: **Medical Advisor Dashboard:** The screenshot shows the 5 different parts of the MA Dashboard: (1) the anonymized worker information, (2) technical status parameters, (3) all gathered values, (4) historical data and sharing possibility controls and (5) feedback channel controls.

shown in (5).

# 6. Limitations and Future Work

CHEST faces several limitations we are currently trying to address. The cooling unit needs to be integrated into the suit using the already developed 3D printed cooling structures. The sensor quality and medical effectiveness needs to be evaluated. The data transmission and the security of the communication channel need to be addressed.

### 7. Conclusion

In this paper we describe CHEST, a Human-Centric Cyber-Physical System. It is a vertical prototype that is designed to monitor and reduce physical stress of workers in harsh, hazardous environments. We could show the technical feasibility and major benefits compared to data logger based systems. We brought together researchers from different domains all contributing with their domain specific knowledge. CHEST supports the process of setting up a mission-team using mobile devices. CHEST allows remote health monitoring, in combination with wearables and smart textiles. Moreover, it includes a feedback channel between all included stakeholders, namely, the worker, the Medical Advisor and the Mission Commander. It includes a context aware secure zone detection so that the Mission Commander knows, which worker returned to the secure zone. We are currently extending the prototype to offer smart cooling capabilities, directly integrated into the system.

### Acknowledgments

Thanks to Aly Saleh, Dimitar Magurev, João Trindade, Josef Seidl, Konstantin Kromer, Richard Otto, Simon Zimmermann and Valeriia Chernenko for their great effort during the project. Special thanks to Florian Dennerlein for the constructive cooperation and support.

# References

- [1] J. Reason. Human Error. Cambridge University Press, 1990.

- [2] Jean-Claude Laprie. Dependable computing and fault-tolerance. Digest of Papers FTCS-15, pages 2–11, 1985.

- [3] M. Sanders and E. McCormick. *Human Factors In Engineering and Design*. McGraw-Hill international editions: Psychology series. McGraw-Hill Education, 1993.

- [4] J. Von Knop. A Process for Developing a Common Vocabulary in the Information Security Area. IOS Press, Amsterdam, The Netherlands, The Netherlands, 2007.

- [5] O. Goloubeva, M. Rebaudengo, M.S. Reorda, and M. Violante. Software-Implemented Hardware Fault Tolerance. Springer US, 2006.

- [6] Raija MT Laukkanen and Paula K Virtanen. Heart rate monitors: state of the art. *Journal of sports sciences*, 16:3–7, 1998.

- [7] Sukun Kim, S. Pakzad, D. Culler, J. Demmel, G. Fenves, S. Glaser, and M. Turon. Health monitoring of civil infrastructures using wireless sensor networks. In *Information Processing in Sensor Networks*, 2007. *IPSN 2007. 6th International Symposium*, pages 254–263, April 2007.

- [8] A. Pantelopoulos and N.G. Bourbakis. A survey on wearable sensorbased systems for health monitoring and prognosis. *Systems, Man, and Cybernetics, Part C: Applications and Reviews, IEEE Transactions on*, 40(1):1–12, Jan 2010.

- [9] Yang Hao and Robert Foster. Wireless body sensor networks for health-monitoring applications. *Physiological measurement*, 29(11):R27–R56, 2008.

- [10] P.J. Soh, G.A.E. Vandenbosch, M. Mercuri, and D.M.M.-P. Schreurs. Wearable wireless health monitoring: Current developments, challenges, and future trends. *Microwave Magazine, IEEE*, 16(4):55–70, May 2015.

- [11] C.W. Mundt, K.N. Montgomery, U.E. Udoh, V.N. Barker, G.C. Thonier, A.M. Tellier, R.D. Ricks, B.B. Darling, Y.D. Cagle, N.A. Cabrol, S.J. Ruoss, J.L. Swain, J.W. Hines, and G.T.A. Kovacs. A multiparameter wearable physiologic monitoring system for space and terrestrial applications. *Information Technology in Biomedicine, IEEE Transactions*, 9(3):382–391, Sept 2005.

- [12] K.J. Glitz, U. Seibel, U. Rohde, W. Gorges, A. Witzki, C. Piekarski, and D. Leyk. Reducing heat stress under thermal insulation in protective clothing: microclimate cooling by a 'physiological' method. *Ergonomics*, 58(8):1461–1469, 2015. PMID: 25679096.

- [13] Juul Achten and Asker E Jeukendrup. Heart rate monitoring. Sports medicine, 33(7):517–538, 2003.

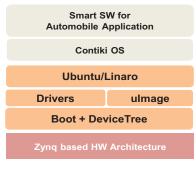

# Thermal-Aware Task Allocation and Scheduling for Heterogeneous Multi-core Cyber-Physical Systems

### Shikang Xu, Israel Koren and C. M. Krishna

Department of Electrical and Computer Engineering University of Massachusetts Amherst, Amherst, MA, 01003

**Abstract**—Over the past few years, the impact of heating on device failure rates has become increasingly important in cyber-physical systems. Such systems are often used in harsh environments and have weight, volume and power constraints which make it hard to dissipate heat economically and effectively. Thermal-aware task scheduling techniques are therefore called for to reduce heat stress on the computational platform.

In this paper, we outline a thermal-aware task allocation and scheduling heuristic for use in computational platforms that feature heterogeneous computational cores. Such systems, consisting typically of some powerful, out-of-order, cores, together with simple, in-order, cores, allow the user a wider range of power-performance tradeoffs than traditional homogeneous multicore systems. We show how using fairly simple thermal-aware task allocation and scheduling principles results in a substantial enhancement in the expected lifetime of the system.

Index Terms—DVFS, Real-time systems, Cyber-physical systems, Lifetime extension, Heterogeneous multi-core

# **1** Introduction

Cyber-physical systems (CPSs) are proliferating in lifecritical and cost-sensitive contexts today. The economical provision of high reliability in such systems is very important.

Thermal stress is an important source of accelerated device aging, resulting in premature device failure. Indeed, failure rates are often modeled as exponentially increasing with absolute temperature. Furthermore, much of the thermallyinduced damage is cumulative, not transient. As technology has advanced and feature sizes have shrunk, heat density has increased, making high temperature an important factor in device degradation and failure.

We focus in this paper on how to allocate and schedule CPS tasks on heterogeneous multi-core platforms, in a thermalaware fashion. Such platforms, such as big.LITTLE from ARM [1], typically consist of high-performance cores with advanced pipelining features for enhanced throughput, coupled with very small cores only capable of simple, in-order, instruction processing. All cores, simple and complex, on the platform share the same instruction set so that task migration across core types is possible. Such platforms are attractive for CPS since they offer an increased flexibility in scheduling dynamically varying real-time workloads [2]–[4].

In this paper, we introduce a simple task allocation and scheduling algorithm for real-time systems using a heterogeneous multi-core platform. The aim is to meet all deadlines while reducing thermal stress. Our simulations show that this algorithm significantly enhances the core Mean Time To Failure (MTTF) over a baseline algorithm.

The rest of the paper is organized as follows. Section 2 reviews related prior work and points out the thermal impact on lifetime and reliability. Section 3.2 contains our algorithm. Simulation results illustrating the performance of this algorithm are presented in Section 4. Section 5 concludes this paper.

# 2 Background

#### 2.1 Related Works

Over the past decade, much work has been conducted on general-purpose, single-ISA, heterogeneous multi-core systems task scheduling [5]–[10]. In [9], Craeynest *et al.* developed a workload-to-core mapping algorithm for single-ISA heterogeneous multi-core processors to improve performance by dynamically monitoring the behavior (through measures like Cycles per Instruction and Instruction-Level Parallelism) of tasks. In [10], Zhang *et al.* proposed an algorithm based on dynamic execution behavior of workloads, to map tasks to cores to achieve higher energy-efficiency while maintaining comparable performance as in [9].

For real-time systems, recent research focuses on algorithms to guarantee an increased amount of workload to be finished before its deadline. Baruah introduced a polynomialtime feasibility analysis method that can determine if a set of real-time tasks can be scheduled on an multi-core system and tasks can migrate between cores [2]. Kim *et al.* proposed a scheduling algorithm for aperiodic hard real-time tasks executing on heterogeneous platforms that restrict tasks to be executed on certain cores according to their expected completion time [11].

Raravi *et al.* showed that, if the tasks can only migrate between the cores of the same type, an optimal algorithm needs cores that are  $1 + \frac{\beta}{2}$  times faster ( $0 < \beta < 1$ ) than in a system where tasks can migrate among multiple core types [3].

Recently, Chwa *et al.* proposed a task scheduling algorithm for real-time systems with two core types [4]. In their algorithm, the cores are assumed to share the same instruction set architecture (ISA) so that tasks can migrate between core types. A two-phase approach is followed: first, assignment of tasks to the appropriate core type, and second, a modified DP(deadline partitioning)-fair [12] method is used to schedule the workload on each type.

This work was partially supported by the National Science Foundation under grant CNS 1329831.

#### 2.2 Thermal Related Reliability and Lifetime

The reliability of VLSI circuits is affected by multiple mechanisms. Modeling these has been an active research topic for decades. Electromigration (EM) and Oxide Breakdown are reported to be dominant permanent failure mechanisms of VLSI circuits as CMOS technology scales [13] and consequently, these are the modes that we focus on.

According to [14], the Mean-Time-To-Failure (MTTF) due to the oxide breakdown process is given by:

$$MTTF_{bd} = A_{bd} * V^{-(a-bT)} * e^{\frac{X+(Y/T)+ZT}{kT}}$$

(1)

where V is the voltage applied to the gate oxide, T is the absolute temperature in Kelvin, k is Boltzmann's constant and  $A_{bd}$  is a scale factor. The values of the other parameters are [14]: a = 78, b = -0.0081, X = 0.759eV, Y = -66.8eV \* K and Z = -8.37e4eV/K. Note that these parameters, or even the MTTF model, can be different as the CMOS manufacture technology developing.

The mechanism behind EM has been studied extensively. One of the early results that is still widely used for estimating the MTTF due to EM, was proposed by Black [15]:

$$MTTF_{em} = A_{em} * J^{-n} e^{\frac{E_a}{kT}}$$

(2)

where  $A_{em}$  is a scale factor, J is the current density,  $E_a$  is activation energy and n is a material based constant. For copper, these values are  $J = 1e^6 A/cm$  [16],  $E_a = 0.9eV$  and n = 1.1 [17].

The failure of a system is a random process and the reliability of a system at time t is the probability that the system is functional throughout the time interval [0, t]. The probability of a device failure occurrence if often modeled by by the Weibull distribution [18]:

$$F(t) = 1 - R(t) = 1 - e^{-(t/\alpha)^{\beta}}$$

(3)

where F(t) is the failure occurrence probability, R(t) is the reliability function,  $\beta$  is the Weibull slope parameter ( $\beta$ =2, [19]), and  $\alpha$  is a scale parameter satisfying  $\alpha = MTTF/\Gamma(1+1/\beta)$ .

The reliability expressions shown above were obtained from a combination of experimental results and proposed physical models. In this paper, the approach of [18] is adopted to calculate the reliability in a dynamic thermal environment (i.e., under varying temperatures). Time is divided into k time frames,  $[0,\Delta t], [\Delta t, 2\Delta t], ..., [(k-1)\Delta t, k\Delta t]$ . Each time frame is short enough so that the temperature and voltage are roughly constant within it. The resulting reliability of a functional block in an IC (e.g., an integer execution unit), denoted by  $R_{blk}(t)$ , is:

$$R_{blk}(t) = R(k\Delta t) = \prod_{i=1}^{i=k} [1 - (R_i((i-1)\Delta t) - R_i(i\Delta t))]$$

(4)

where  $R_i(i\Delta t) = R_{i_{em}}(i\Delta t) * R_{i_{bd}}(i\Delta t)$ ;  $R_{i_{em}}(i\Delta t)$  and  $R_{i_{bd}}(i\Delta t)$  are the reliabilities due to electromigration and oxide breakdown, respectively, and are calculated by Equation 3 using the MTTFs derived from the reliability model using the temperature of the *i*th time interval.

The reliability of a core at time t is the product of the reliability of all the functional blocks of the core at time t.

# **3** Thermal Aware Heterogeneous Multicore Scheduling Algorithm

#### 3.1 System Models

The heterogeneous multi-core system we consider consists of two core types: out-of-order ("big") and in-order ("small") cores. The former are much more complicated, with sophisticated pipelining techniques to improve performance (at the cost of power consumption); the latter are simple and slow. All cores use the same instruction set architecture, meaning that tasks can, deadlines permitting, execute on any core. All cores of the same type are identical to one another. As already mentioned, this structure is commercially realized these days, one example being the ARM big.LITTLE architecture.

The task set is periodic, with deadlines equal to the period. This is a common model for real-time systems in practice [20]; we will later extend it to the case where deadlines are constrained to be less than or equal to their period. Each task  $\tau_i$  is characterized by the following three parameters: period  $(p_i)$ , Worst-Case Execution Time (WCET) on a big core  $(e_i^b)$  and WCET on a small core  $(e_i^s)$ . In this paper, it is assumed that for all  $\tau_i$ ,  $e_i^b \leq e_i^s$  and the utilization on the big core satisfies  $u_i^b = \frac{e_i^b}{p_i} \leq 1$ . If the utilization on small core,  $u_i^s = \frac{e_i^s}{p_i}$ , is larger than 1, only using small cores is insufficient to meet the worst-case computational demands of the workload. Tasks can be migrated from one core to another during execution.

We also assume that the cores share the main memory and last level cache (LLC). With this assumption, the task migration overhead is negligible [9]. For systems with manycores, the assumption may not be true. However, cores are usually clustered into groups that share LLC and memory. The proposed algorithm can be applied to the cores that are lie in the same group.

The reliability figure-of-merit we use is the product of the individual reliabilities of all the cores. The expected lifetime of the system is defined as the point at which this figure of merit declines to a predetermined level.

#### 3.2 Task Assignment and Scheduling

#### 3.2.1 Baseline Algorithm

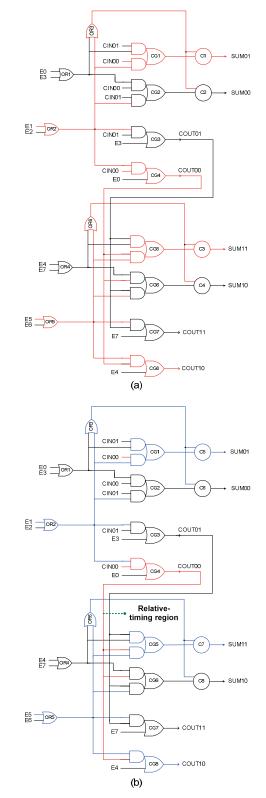

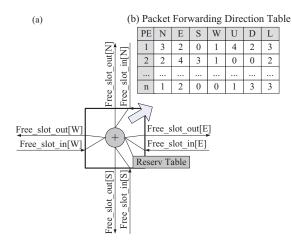

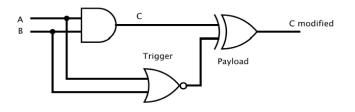

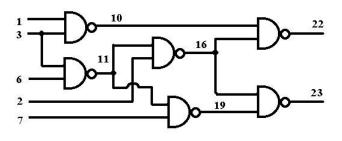

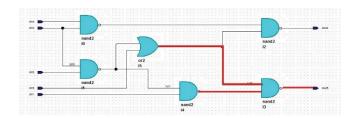

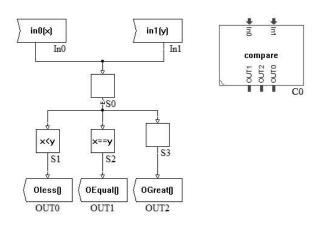

To provide appropriate context for our work, we start with a brief description of a baseline multicore scheduling algorithm. As already mentioned, Chwa, *et al.*, propose an optimal task scheduling algorithm for heterogeneous multi-core real-time systems. Two core types are assumed [4]. Optimality is demonstrated by proving that as long as a task set can be feasibly scheduled on a heterogeneous multi-core system, it can be scheduled by their algorithm. The algorithm proposed in [4] includes two phases: workload assignment (Hetero-Split) and schedule generation (Hetero-Wrap). A high-level description is shown in Figure 1. In [4], it is assumed that some tasks will execute faster on type-I cores while other tasks will execute faster on type-I cores that executes it slower can be greater than 1, there is a minimum fraction of such a task that must be executed on

#### Notation:

$e_i^1/e_i^2$ : WCET of  $\tau_i$  on type-I/II core  $\Gamma_i^1/\Gamma_i^2$ : list of tasks on type-I/II core  $x_i^1/x_i^2$ : portion of  $\tau_i$  on type-I/II core  $\begin{array}{l} M_1': \text{ list of tasks } u_i^1 * x_i^1 + u_i^2 * x_i^2 = 1 \text{ and } x_i^1 > 0, x_i^2 > 0 \\ M_2: \text{ list of tasks } u_i^1 * x_i^1 + u_i^2 * x_i^2 < 1 \text{ and } x_i^1 > 0, x_i^2 > 0 \end{array}$  $P_1/P_2$ : list of tasks only assigned to type-I/II cores **Hetero-Split:**

calculate minimum fraction of each task i on the faster core using equation (5) and (6)

$\Gamma^{1} \leftarrow \{\tau_{i} | e_{i}^{1} < e_{i}^{2}\}, \ \Gamma^{2} \leftarrow \{\tau_{i} | e_{i}^{2} < e_{i}^{1}\}$

IF workload on type-I (type-II) cores is larger than its capacity

#### repeat

find the  $\tau_k$  with the smallest (largest)  $\frac{e_i^1}{e_i^2}$ move  $\tau_k$  to type-II (type-I) cores  $(lo_k^1 \ (lo_k^2)$  cannot be moved)

Until workload on type-I (type-II) cores is no larger than its capacity

#### Hetero-Wrap:

For tasks in  $M_1$ ,  $M_2$  and  $P_1$

fill the type-I cores' slices from the beginning of slice For tasks in  $M_1$ ,  $M_2$  and  $P_2$

fill the type-II cores' slices from the end of slice

Fig. 1. General flow of the algorithm in [4]

the other core type. This minimum fraction (denoted by  $lo_i$ ) is calculated in the following way:

$$lo_{i}^{1} = \begin{cases} \frac{u_{i}^{2}-1}{u_{i}^{2}-u_{i}^{1}}, & \text{if } u_{i}^{2} > 1\\ 0, & \text{otherwise} \end{cases}$$

(5)

$$lo_i^2 = \begin{cases} \frac{u_i^1 - 1}{u_i^1 - u_i^2}, & \text{if } u_i^1 > 1\\ 0, & \text{otherwise} \end{cases}$$

(6)

where  $u_i^1(u_i^2)$  is the utilization on Type I (Type II) core.

In the task assignment phase, the workload is assigned to the different core types. The first step is to determine the minimum portion of each task that needs to be executed on the type of core that executes it faster and allocate that portion to such a type. If the workload assigned to any type of core is more than its ability to schedule after such an assignment, then the algorithm cannot schedule the task set. The second step will initially assign the rest of the workload (tasks with utilization smaller than 1 on both types cores and tasks with utilization larger than 1 on one type of core excluding the portion dealt with in first step) to the type of core that can execute it faster. If there is a type of core that cannot finish its assigned workload on time, the task will then be moved to the other core type. The order at which tasks are moved is determined by the ratio of execution times on the two core types for each task, e.g., when moving from type-I to type-II core, the task with the largest  $\frac{e_i^1}{e_i^2}$  will be moved first. But if the moving task has a portion that must be executed on current core (from equation (5) and (6)), this portion will not be moved.

In the phase of schedule generation, the algorithm is a modification of DP-fair [12]. The execution is divided into slices and each task will be executed for an interval that equals the product of its utilization on the current core and slice length, e.g.,  $\tau_i$  will be executed for 5 seconds on a type-I core if the slice is 10 seconds and  $\tau_i$  has a utilization of 0.5 on type-I core. The situation where a task is scheduled to be executed on two types of cores at the same time needs to be avoided. Tasks are divided into four groups:  $M_1$  are the tasks where the sum of utilization on the two core types equals 1;  $M_2$  are tasks where the sum of the utilization on the two core types is less than 1;  $P_1$  are tasks that are only assigned to type-I cores and  $P_2$  are tasks that are only assigned to type-II cores. The time-slices of type-I cores will be assigned to tasks in the order of  $M_1$ ,  $M_2$  and  $P_1$  from the *beginning* of each slice. The time-slices of type-II cores will be assigned to tasks in the order of  $M_1$ ,  $M_2$  and  $P_2$  from the *end* of each slice.

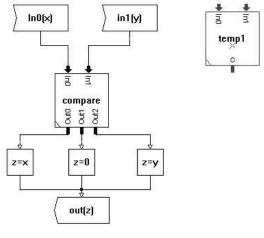

#### 3.2.2 Thermal-Aware Task Allocation and Scheduling

The baseline algorithm described above does not take thermal considerations into account. We describe here a thermalaware task allocation and scheduling algorithm, which we will then show has significant lifetime-enhancement benefits. The system model assumed was described in Section IIIA, namely, we assume "smaller" and "bigger" cores. Smaller cores do not have performance-enhancing (but power-hungry) features like out-of-order execution.

The general principle behind this algorithm is to preferentially assign load to the smaller cores; only that portion of a task that cannot feasibly be executed on the smaller cores is assigned to the bigger core. Second, we use offline task profiling to obtain the average temperature  $(T_{avg}^i)$  when running a task on a big core. When some tasks have to be assigned to big cores, instead of choosing the task with smallest  $\frac{e_i^b}{e_i^s}$  as in [4], we choose the task with smallest  $T_{avg}^i * \frac{e_i^b}{e_i^s}$ . (Note: this modification will potentially sacrifice optimality.)

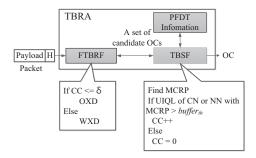

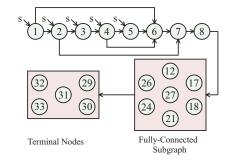

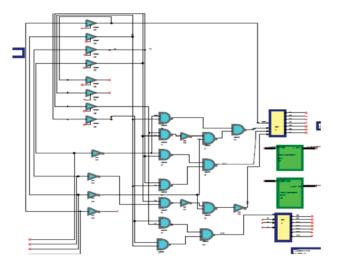

The pseudo code of the thermal-aware task assignment is shown in Figure 2. In stage 1, the minimum fraction of each task that needs to be executed on big cores is allocated to big cores. If the big cores cannot execute the allocated minimum workload, the given task sets cannot be scheduled, and the algorithm returns failure. In stage 2, all the remaining workload is assigned to small cores. In stage 3, if the small cores cannot schedule the assigned workload, some workload needs to be moved to the big cores. In the workload reassignment, the task  $\tau_k$  with the smallest product of  $\frac{e_i^s}{e_i^b}$  and the average execution temperature on the big core will be moved first. If the small cores still cannot schedule the workload on them after moving the whole task, the whole  $\tau_k$  will be moved to big cores. Otherwise, the algorithm only moves that part of the task such that the small cores can schedule the workload on them. Once the task assignment to cores is successfully determined according to this process, the Hetero-wrap scheduling procedure from the baseline algorithm is used to generate the task schedule.

#### **3.3 DVFS** Algorithm

Dynamic Voltage and Frequency Scaling (DVFS) has long been used to reduced the thermal impact on processors. In

#### Notation

$u_i^b/u_i^s$ : utilization of  $\tau_i$  on big/small core  $x_i^b/x_i^s$ : fraction of  $\tau_i$  assigned to big/small core  $lo_i$ : minimum fraction of  $\tau_i$  assigned to big core  $y_i^b/y_i^s$ : fraction of  $\tau_i$  assigned to big/small core excluding  $lo_i$  $\Gamma_b/\Gamma_s$ : list of tasks on big/small core  $m_b/m_s$ : number of big/small cores  $er_i: T_{avg}^i * \frac{e_i^s}{e_i^b}$  of  $\tau_i$ Task\_ alloc(T) Stage 1: Allocate  $lo_i$ if  $\sum lo_i * u_i^b > m_b$ return not feasible Stage 2: for all  $\tau_i$  in T  $\Gamma_s \leftarrow \Gamma_s \cup \tau_i$  $y_i^s \leftarrow 1 - lo_i$ Stage 3:  $\begin{array}{l} \text{if } \tilde{\sum} y_i^s \ast u_i^s \leq m_s \\ \text{return } \{x_i^b | x_i^b = lo_i\}, \{x_i^s | x_i^s = y_i^s\} \end{array}$ else while  $\sum y_i^s * u_i^s > m_s$ find  $\tau_k$  with smallest  $er_i$  in  $\Gamma_s$  $\begin{array}{l} \text{if } \sum\limits_{y_k^s} y_i^s \ast u_i^s - y_k^s \ast u_k^s > m_s \\ y_k^b \leftarrow 1 - lo_k \end{array}$

$$\begin{split} y_k^b &\leftarrow 1 - lo_k \\ y_k^s &\leftarrow 0 \\ \Gamma_s &\leftarrow \Gamma_s - \tau_k \\ \textbf{else} \\ y_k^b &\leftarrow \frac{\sum y_i^s \ast u_i^s - m_s}{u_k^s} \\ y_k^s &\leftarrow 1 - lo_k - y_k^b \\ \textbf{if } \sum y_i^b \ast u_i^b &> m_b - \sum lo_i \ast u_i^b \\ \textbf{return not feasible} \\ \textbf{return } \{x_i^b | x_i^b = lo_i + y_k^b\}, \{x_i^s | x_i^s = y_i^s\} \end{split}$$

Fig. 2. Thermal Aware task assignment

[21], a DVFS scheme based on Instructions-Per-Clock (IPC) monitoring is presented to improve the lifetime of processors by preferentially using slack to slowdown a high-IPC phase of workload. When executing tasks according to the slice schedule generated using the method described above, DVFS is applied using the concept proposed in [21].

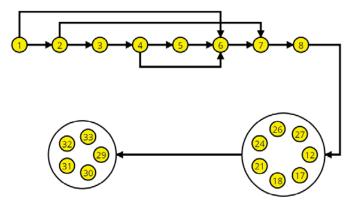

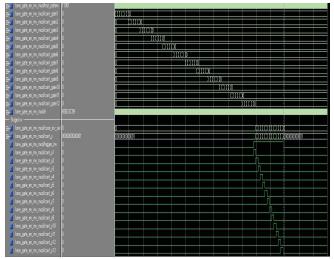

As stated above, there are partitioned tasks and migrating tasks on cores. Applying DVFS on migrating tasks may result in executing the same task on different cores at the same time, which is not allowed. Thus, in this paper, only partitioned tasks are subject to slowdown by voltage scaling. The pseudo code of the DVFS algorithm is shown in Figures 3 and 4. In Figure 3, at the beginning of every time step, the tasks completed in the prior time step are indicated using a finishing flag array. If a new iteration of a task is released, this flag is reset. Also, at the beginning of each time slice, the schedule is rearranged based on current uncompleted tasks in the system; the available slack in the coming time slice is then calculated. The initial task assignment and scheduling is based on the Worst Case Execution Time (WCET) of each task. If a task finishes earlier than its WCET, there is no need to allocate time for this task in the coming time slices until its next iteration is released.

## Algorithm: IPC DVFS

```

Notation:

T_{sys}: Tasks in system

P: list of partitioned tasks on core

t_{sys}: system time, initialized at 0

f_{high}/f_{low}: processor high/low frequency level

\Delta t: time step

t_{slice}: length of scheduling slice

F: flag array indicating if task i has finished the current

iteration

IPC: Array recording the IPC of \tau_i in the previous time

step

SA: schedule array for core in each slice after task

assignment

At every time step

For each \tau_i in system

IF \tau_i finished in past \Delta t

F[i] = 1

IF t_{sim} \mod p_i=0

F[i] = 0

IF t_{sim} \mod t_{slice} = 0

For all \tau_i in T_{sys}

IF F[i]=0

T \leftarrow T \cup \tau_i

Task\_Alloc(T)

Generate SA for each core

Alloc\_Slack()

Set count=0 on each core

On each core

execute \tau_{SA[count].index} at speed SA[count].speed

set IPC[SA[count].index] to IPC in the \Delta t

```

IF  $t_{sys} \mod t_{slice}$ =SA[count].end or task finishes count+=1

#### Fig. 3. IPC based DVFS

Thus, at the beginning of every time slice, tasks that have not finished will be reassigned using the task assignment algorithm described in the previous section. Then, the slack will be used to slow down partitioned tasks on big cores using the algorithm shown in Figure 4.

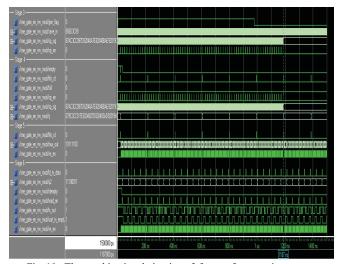

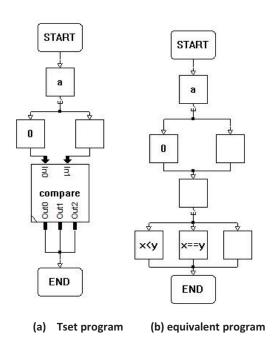

On big cores, the partitioned tasks are arranged to be executed first in the coming time slices. Firstly, all the uncompleted partitioned are clustered to the front part of the slice and all the uncompleted migrating tasks are clustered to the end part of the slice. The gap between these two clusters is the available slack. As is shown in Figure 4, the IPC of each task in the prior time step is recorded. The available slack is then allocated to the task with the highest IPC. Based on how much slack is available, the task with highest IPC in a given time slice is either wholly or partially slowed down. If there is still some slack left after the above process, the task with the second highest IPC will go through the same process. This process continues until the slack is used up or all partitioned tasks are slowed down.

#### Notation

*P*: list of partitioned tasks  $f_{high}/f_{low}$ : high/low frequency level of core SA[i].index: index of task that is at position i of array SA SA[i].start: start time of the task at position i SA[i].end: end time of the task at position i

SA[i].end. end time of the task at position TSA[i].speed: frequency level to run task position i

### Alloc\_Slack()

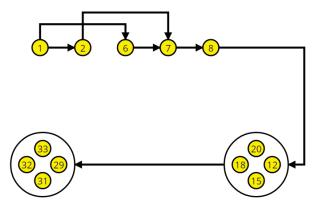

On each big core  $\Gamma_p = \{SA[i] | SA[i].index \in \mathbb{P}\}$ front=0, end= $t_{slice}$ FOR i in (0..SA.size-1) IF  $SA[i] \in \Gamma_p$ *l*=SA[i].end-SA[i].start SA[i].start=front SA[i].end=front+l front=SA[i].end FOR i in (SA.size-1..0) IF  $SA[i] \notin \Gamma_p$ *l*=SA[i].end-SA[i].start SA[i].end=end SA[i].end=end-l end=SA[i].start slack=end-frontFOR SA[i] in  $\Gamma_p$ *laccess in IPC in past*  $\Delta t$  *descending order* l=SA[i].end-SA[i].start  $sn=1*\frac{f_{high}-f_{low}}{f_{low}}$ //slack needed to slowdown the how part of SA[i] IF slack>sn SA[i].speed=LV SA[i].end+=sn rearrange SA[k]s following SA[i] in SA slack-=sn ELSE IF slack>0  $\begin{array}{l} {\rm sp=slack}*\frac{f_{low}}{f_{high}-f_{low}}\\ //workload\ can\ be\ slowed\ by\ slack \end{array}$ SA[i].speed=LV SA[i].end=SA[i].start+slack+sp insert (index=SA[i].index, speed=LV, start=SA[i].end, end =start+l-sp) to SA rearrange SA[k]s following SA[i] in SA slack=0 ELSE break

Fig. 4. Slack allocation on big core

# 4 Experimental Results

### **4.1 Experiment Setup**

A system with one out-of-order (big) core and one inorder (small) core is simulated to compare the thermal-aware algorithm introduced in the previous section to the baseline algorithm. The big core has two frequency levels: 2.0 GHz and 1.2 GHz. Applications from the Mibench benchmark suite [22] are used as a workload of independent tasks. Task sets are generated by selecting five tasks randomly from the benchmark suite. The WCET for each task running on big/small core of each task is found by using the Gem5 [23] out-of-order/inorder simulator. The actual execution time of each iteration is a random number; it is selected to be normally distributed with mean equal to half the WCET and standard deviation of 0.2 of the mean, conditioned to be no greater than the WCET value.

To obtain the power consumption of the workload we used Gem5 and MaPAT [24]. These power traces were then used to generate temperature traces for each of the cores; we used the fast thermal simulator TILTS [25] which is a modification of HotSpot [26]. When a task has an actual execution time that equals  $r_i$  of its WCET, its power file will be compressed in the time domain to this fraction. This ensures simulation of all the high/low power phases in the execution of a task.

The reliability of each core (thus the system) is initially set to 1. Recall that our figure-of-merit (FOM) is the operating time before the reliability of the system (i.e., the product of the individual core reliabilities) reaches a given threshold; we illustrate here the lifetimes when the FOM thresholds are  $1 - 10^{-6}$ ,  $1 - 10^{-7}$ , and  $1 - 10^{-8}$ , respectively. Corresponding lifetimes are evaluated for the task schedule generated by the baseline algorithm and the improvement of our algorithm over the baseline is calculated.

A simple partitioned algorithm is also introduced to be compared with the algorithm proposed in this paper. Using the partitioned algorithm, each task is statically assigned to core and can only be executed on that core. On each core, earliest deadline first (EDF) [20] is used to schedule tasks.

### **4.2 Numerical Results**

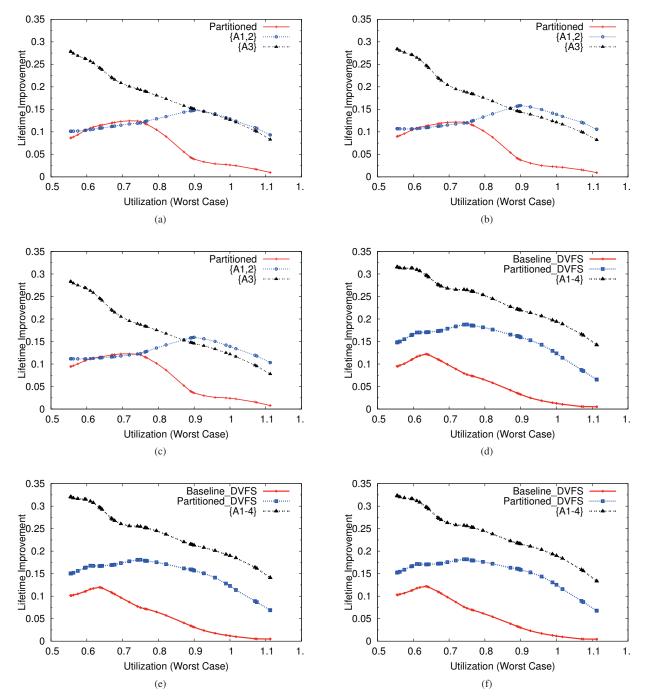

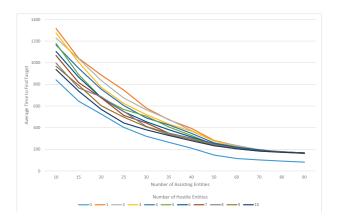

Recall the main steps we used to enhance reliability in this algorithm: (A1) Assign workload to small cores as much as possible; (A2) When some tasks need to be executed on big cores, tasks that execute faster and have a lower thermal impact on big cores are assigned to big cores first; (A3) Perform workload reassignment when a task finishes before its WCET, and (A4) Use dynamic voltage and frequency scaling so long as that can be done without causing tasks to be executed on more than one core at the same time. We carry out experimental studies to evaluate the impact of these approaches on lifetime enhancement.

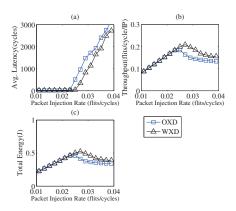

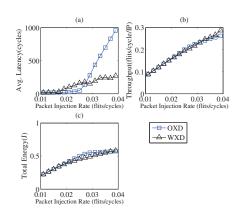

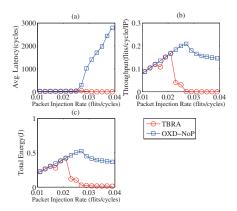

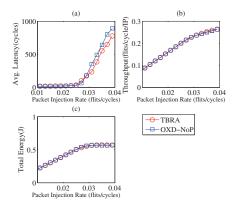

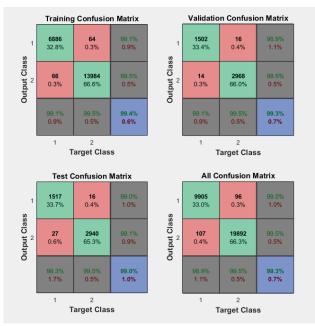

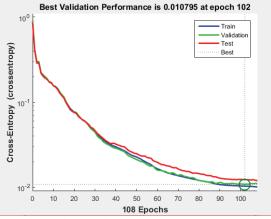

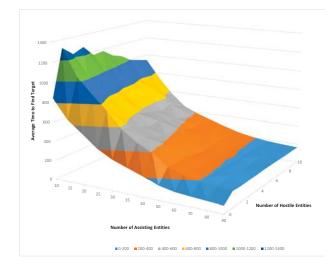

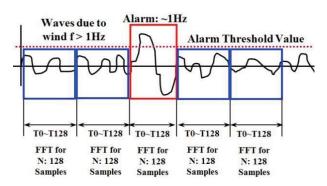

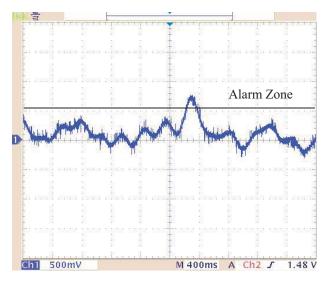

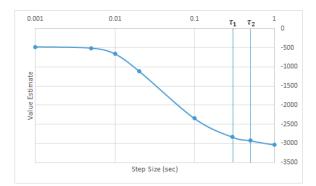

In Figure 5(a)-(c), the lifetime improvement without DVFS (thus using A1, A2 and A3) at different system reliabilities is shown. As already stated, the algorithm in [4] is used as baseline. "Partitioned" stands for the simple static algorithm. "A1,2" indicates that our algorithm is using A1 and A2. "A3" indicates that the algorithm is using A3. The x-axis, utilization (Worst Case), is the utilization of the task sets on the big core when the execution times of tasks equal to WCET. As shown in Figure 5, when the utilization is low, all algorithms show gains over the baseline. This is because the baseline algorithm assigns all tasks to the big core while other algorithms will assign tasks to the small core. Using A3 gains as much as 27% improvement under low utilization; under these conditions, using task reassignment, there are more chances to reassign a task to the small core and ease the thermal impact on the big core. Thus, the lifetime of the system is improved greatly. At high utilization, using A1 and A2 performs better and gains more than 10% of improvement. This is because when the system is almost fully utilized, the order in which tasks are

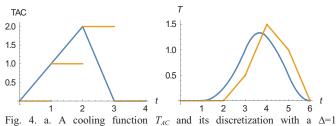

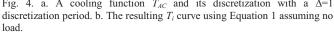

Fig. 5. Improvement for different reliability thresholds: (a) Reliability of 1-1e8 (b) Reliability of 1-1e7 (c) Reliability of 1-1e6 Improvement for different reliability thresholds with DVFS: (d)Reliability of 1-1e8 (e) Reliability of 1-1e7 (f) Reliability of 1-1e6

assigned can more effectively control the thermal impact on cores; note that under these conditions, there will not be much slack for reassignment with dense workload.

Figures 5(d)-(f) show the improvement at different system reliabilities when voltage scaling is used. "Baseline\_DVFS" stands for the baseline algorithm with DVFS. The baseline algorithm in [4] does not use DVFS. We add the DVFS capability by evenly assigning the slack generated by early completion to uncompleted tasks that only executed on the

big core. "Partitioned\_DVFS" uses the DVFS algorithm in [27]. "A1-4" uses all the 4 techniques and the algorithm we proposed in this paper. As is shown in Figures 5(d)-(f), using the techniques and algorithm proposed in this paper, the lifetime improvement is much higher than other algorithms. At high utilization, since the baseline algorithm tends to assign as much workload to the big core as possible, there is only a little slack available to apply DVFS and result in a minimal lifetime improvement. The proposed approach (using the A1-

4 techniques), on the other hand, assigns less workload to the big core, gets more slack and applies slack to tasks with higher thermal impact. These result in the the highest lifetime improvement among the three approaches. When the utilization is low, there is even more slack for DVFS on the big core using the proposed approach. Thus, the improvement over the other two is even higher.

Also note, as is shown in Figure 5, that the lifetime improvements achieved by the proposed approach at different reliabilities are almost identical.

# 5 Conclusion

Thermal issues have emerged as a key consideration in the management of cyber-physical systems. One increasingly popular architecture configuration uses high-end and low-end processing cores on a chip, sharing lower level cache and main memory. Such a mix allows the user a greater range of performance-to-power and performance-to-temperature tradeoffs.

In this paper, we have introduced a thermal-aware task allocation and scheduling heuristic for use in periodic task workloads running on such heterogeneous platforms. Simulation experiments show that this heuristic provides substantial reliability benefits. In future work, we plan to extend this algorithm to cover sporadic tasks as well.

# References

- (ARM 2013) "big.little technology: The future of mobile. [Online]. Available: https://www.arm.com/files/pdf/big\_LITTLE\_Technology\_ the\_Futue\_of\_Mobile.pdf

- [2] S. Baruah, "Feasibility analysis of preemptive real-time systems upon heterogeneous multiprocessor platforms," in *Real-Time Systems Symposium*, 2004. Proceedings. 25th IEEE International, Dec 2004, pp. 37–46.

- [3] G. Raravi, B. Andersson, K. Bletsas, and V. Nlis, "Outstanding paper award: Task assignment algorithms for two-type heterogeneous multiprocessors," in *Real-Time Systems (ECRTS)*, 2012 24th Euromicro Conference on, July 2012, pp. 34–43.

- [4] H. S. Chwa, J. Seo, J. Lee, and I. Shin, "Optimal real-time scheduling on two-type heterogeneous multicore platforms," in *Real-Time Systems Symposium*, 2015 IEEE, Dec 2015, pp. 119–129.

- [5] R. Kumar, D. M. Tullsen, P. Ranganathan, N. P. Jouppi, and K. I. Farkas, "Single-isa heterogeneous multi-core architectures for multithreaded workload performance," in *Computer Architecture, 2004. Proceedings. 31st Annual International Symposium on*, June 2004, pp. 64–75.

- [6] T. Li, D. Baumberger, D. A. Koufaty, and S. Hahn, "Efficient operating system scheduling for performance-asymmetric multi-core architectures," in *Supercomputing*, 2007. SC '07. Proceedings of the 2007 ACM/IEEE Conference on, Nov 2007, pp. 1–11.

- [7] J. C. Mogul, J. Mudigonda, N. Binkert, P. Ranganathan, and V. Talwar, "Using asymmetric single-isa cmps to save energy on operating systems," *IEEE Micro*, vol. 28, no. 3, pp. 26–41, May 2008.

- [8] D. Shelepov, J. C. Saez Alcaide, S. Jeffery, A. Fedorova, N. Perez, Z. F. Huang, S. Blagodurov, and V. Kumar, "Hass: A scheduler for heterogeneous multicore systems," *SIGOPS Oper. Syst. Rev.*, vol. 43, no. 2, pp. 66–75, Apr. 2009.

- [9] K. V. Craeynest, A. Jaleel, L. Eeckhout, P. Narvaez, and J. Emer, "Scheduling heterogeneous multi-cores through performance impact estimation (pie)," in *Computer Architecture (ISCA), 2012 39th Annual International Symposium on*, June 2012, pp. 213–224.

- [10] Y. Zhang, L. Duan, B. Li, L. Peng, and S. Sadagopan, "Energy efficient job scheduling in single-isa heterogeneous chip-multiprocessors," in *Quality Electronic Design (ISQED), 2014 15th International Sympo*sium on, March 2014, pp. 660–666.

- [11] S. I. Kim, J.-K. Kim, H. U. Ha, T. H. Kim, and K. H. Choi, "Efficient task scheduling for hard real-time tasks in asymmetric multicore processors," in *Proceedings of the 12th International Conference on Algorithms and Architectures for Parallel Processing - Volume Part II*, ser. ICA3PP'12. Springer-Verlag, 2012, pp. 187–196.

- [12] G. Levin, S. Funk, C. Sadowski, I. Pye, and S. Brandt, "Dp-fair: A simple model for understanding optimal multiprocessor scheduling," in *Real-Time Systems (ECRTS), 2010 22nd Euromicro Conference on*, July 2010, pp. 3–13.

- [13] J. Srinivasan, S. Adve, P. Bose, and J. Rivers, "The impact of technology scaling on lifetime reliability," in *Dependable Systems and Networks*, 2004 International Conference on, June 2004, pp. 177–186.

- [14] J. Srinivasan, S. V. Adve, P. Bose, S. V. A. P. Bose, and J. A. Rivers, "The case for lifetime reliability-aware microprocessors," in *In Proc. of the 31st International Symposium on Computer Architecture*, 2004, pp. 276–287.

- [15] J. R. Black, "Mass transport of aluminum by momentum exchange with conducting electrons," in *Reliability Physics Symposium*, 2005. *Proceedings. 43rd Annual. 2005 IEEE International*, April 2005, pp. 1–6.

- [16] Z. Lu, W. Huang, M. Stan, K. Skadron, and J. Lach, "Interconnect lifetime prediction with temporal and spatial temperature gradients for reliability-aware design and run 134 time management: Modeling and applications. very large scale integration (vlsi) systems," *IEEE Transactions on*, 2006.

- [17] J. Srinivasan, S. Adve, P. Bose, and J. Rivers, "Lifetime reliability: toward an architectural solution," *Micro, IEEE*, vol. 25, no. 3, pp. 70– 80, 2005.

- [18] C. Zhuo, D. Sylvester, and D. Blaauw, "Process variation and temperature-aware reliability management," in *Design, Automation Test* in Europe Conference Exhibition (DATE), 2010, 2010, pp. 580–585.

- [19] E. Wu, J. Su, W. Lai, E. Nowak, J. McKenna, A. Vayshenker, and D. Harmon, "Interplay of voltage and temperature acceleration of oxide breakdown for ultra-thin gate oxides," *Solid-State Electronics*, vol. 46, no. 11, pp. 1787 – 1798, 2002.

- [20] J. Liu, Real-Time Systems. Prentice Hall, 2000.

- [21] S. Xu, I. Koren, and C. Krishna, "Improving processor lifespan and energy consumption using dvfs based on ilp monitoring," in *Green Computing Conference and Sustainable Computing Conference (IGSC)*, 2015 Sixth International, Dec 2015, pp. 1–6.

- [22] M. R. Guthaus, J. S. Ringenberg, D. Ernst, T. M. Austin, T. Mudge, and R. B. Brown, "Mibench: A free, commercially representative embedded benchmark suite," in *Workload Characterization*, 2001. WWC-4. 2001 IEEE International Workshop on, Dec 2001, pp. 3–14.

- [23] N. Binkert, B. Beckmann, G. Black, S. K. Reinhardt, A. Saidi, A. Basu, J. Hestness, D. R. Hower, T. Krishna, S. Sardashti, R. Sen, K. Sewell, M. Shoaib, N. Vaish, M. D. Hill, and D. A. Wood, "The gem5 simulator," *SIGARCH Comput. Archit. News*, vol. 39, no. 2, pp. 1–7, Aug. 2011.

- [24] S. Li, J. H. Ahn, R. Strong, J. Brockman, D. Tullsen, and N. Jouppi, "Mcpat: An integrated power, area, and timing modeling framework for multicore and manycore architectures," in *Microarchitecture*, 2009. *MICRO-42. 42nd Annual IEEE/ACM International Symposium on*, Dec 2009, pp. 469–480.

- [25] Y. Han, I. Koren, and C. M. Krishna, "Tilts: A fast architectural-level transient thermal simulation method." *J. Low Power Electronics*, vol. 3, no. 1, pp. 13–21, 2007.

- [26] W. Huang, S. Ghosh, S. Velusamy, K. Sankaranarayanan, K. Skadron, and M. Stan, "Hotspot: a compact thermal modeling methodology for early-stage vlsi design," *Very Large Scale Integration (VLSI) Systems, IEEE Transactions on*, vol. 14, no. 5, pp. 501–513, May 2006.

- [27] P. Pillai and K. G. Shin, "Real-time dynamic voltage scaling for lowpower embedded operating systems," *SIGOPS Oper. Syst. Rev.*, vol. 35, no. 5, pp. 89–102, Oct. 2001.

# Application of Kalman Filter to Estimate Position of a Mobile Node in Indoor Environments

Mounika S. K. Gudipati and Shivakumar Sastry Department of Electrical and Computer Engineering The University of Akron, Akron OH 44325-3904, USA

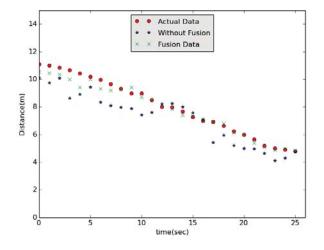

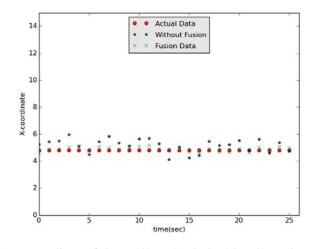

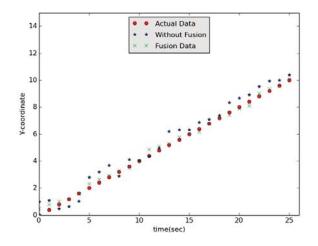

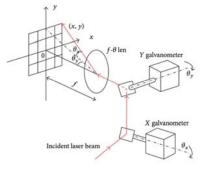

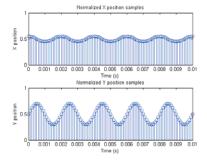

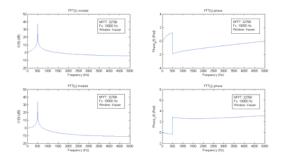

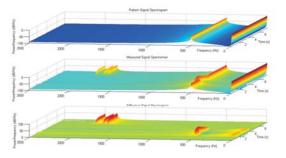

**Abstract**—Indoor location estimation is an important problem for many emerging applications that involve networked embedded systems. We present an approach to estimate the location of a mobile node using a Kalman Filter. The system model comprises four anchor nodes and one or more mobile nodes. Each mobile node uses the average value of the received signal strength to each anchor node to estimate its position using an extended Kalman Filter. These data are fused with data from a local accelerometer to improve the estimate. We present experimental results to demonstrate the precision of our location estimates. In the future, this work can be extended to reduce the error in the location estimates.

*Index Terms*—Extended Kalman Filter, Position Estimation, MultiSensor Fusion.

#### **1** INTRODUCTION

Estimating the position of mobile entities is an important problem for several emerging applications in areas such as advanced manufacturing, Internet of Things, and healthcare systems. The problem is especially challenging when it must be addressed indoors and with high precision. To address this problem, we designed and carried out experiments to understand how much precision could be achieved for position estimation in indoor environments using commercial, lowpower WSN devices.

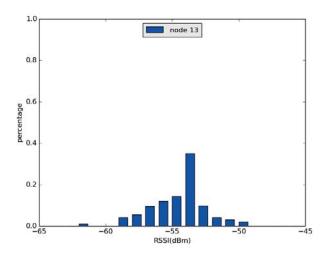

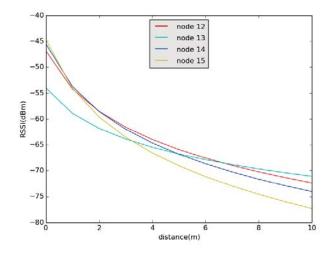

The problem of localization is very well studied in the literature [1], [2], [3]. For example, the GPS system and route navigation is widely used across the world. This problem, however, remains challenging when the resolution of the localization must be high. The localization methods in the literature are based on measuring the distance between a mobile node and a fixed set of anchor nodes at known positions. The distance between the nodes can be calculated using ToA (Time of Arrival), AoA (Angle of Arrival) or RSSI (Received Signal Strength Indicator). While the ToA and AoA can provide more accurate estimates, these approaches rely on additional hardware that are expensive. It is also not clear how much resolution these approaches can offer in laboratory and manufacturing environments that are indoor.

Several reports in the literature address this problem by using the received signal strength and triangulation based on a fixed set of anchor nodes. The option to use RSSI to estimate distance, while attractive, is complicated because of the irregularity of RF propagation in the low-power regime and because the RSSI measurements are noisy.

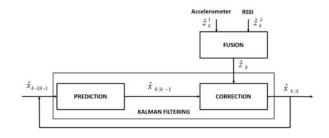

To address the issue of noise, we utilized an Extended Kalman Filter. A Kalman Filter is a widely used recursive prediction-update based state estimator algorithm that can minimize error variance [4]. Thus, by viewing the position of the mobile node as its state, our aim was to minimize the error in the position estimates. The prediction and update steps are combined via the Kalman gain which is calculated in each step to minimize the mean-square error. Such approaches are widely-reported in the literature in several areas including robot localization,guidance and navigation and tracking[5], [6], [7], [8].

The Kalman Filter is, however, known to provide an optimal estimate of the unknown state for a linear dynamic system with Gaussian distribution. The measurements required to assess the state of the mobile node were non-linear. To cope with this challenge, we used an Extended Kalman Filter. This framework allowed us to improve the accuracy of the position estimates, further, by integrating data from accelerometers mounted on the mobile node [9]. Kalman Filters applications for fusing data have also been have also been used widely in the literature to fuse data from multiple sensors [10], [11]. Following these methods, we designed an approach to fuse the data from an accelerometer on the mobile node with the received signal strength data.

While there are several reports in the literature that are based on simulation results, we found the following reports that were based on experiments [12], [13], [14]. Thus, the main focus of this work was to design and carryout experiments to understand how much precision could be achieved for indoor position estimation when using commercial WSN nodes that provide RSSI estimates, with no additional hardware, and when the data from a local accelerometer were fused with the data from the RSSI measurements.

The remainder of this paper is organized as follows. In Section 2 we describe the problem precisely and present the design used. After describing the localization approach in Section 3, we present results from our experiments in Section 4. Finally, we present our conclusions and next steps in Section 5.

#### **2 PROBLEM STATEMENT AND DESIGN**

In this section we describe the system model, the development platform, the measurement inputs, their calibration, and how Kalman Gain was computed.

#### 2.1 System Description

The system comprises a single mobile mote and four anchor motes. Each mote was equipped with wireless transceiver that can periodically transmit data. The mobile mote transmitted data with a known transmission power to the anchor motes. The motes, located within the transmission range of the mobile mote calculate the received RSSI values. The mobile mote was also equipped with accelerometer which was used to record the mote's inertial data.

2.1.1 Development Platform: The IRIS mote was used as the platform to carry out the experiments. This mote has an 8-bit ATMega1281 microcontroller that is optimized for low power operations and can be easily programmed using the C language. The wireless communication between nodes is based on an AT86RF230, IEEE 802.15.4 compliant, transceiver operating in 2.5GHz ISM band. The microcontroller and the transceiver exchange information via the SPI protocol. This mote was used both as the anchor nodes and as the mobile node.

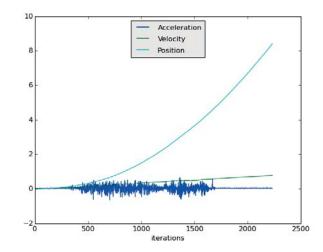

2.1.2 System Model: The state of the mobile node was modeled in terms of its position, velocity and acceleration in a two-dimensional space  $\mathbf{X}_{\mathbf{k}} = [\mathbf{x}, \mathbf{y}, \mathbf{v}_{\mathbf{x}}, \mathbf{v}_{\mathbf{y}}, \mathbf{a}_{\mathbf{x}}, \mathbf{a}_{\mathbf{y}}]$ .<sup>T</sup>

Due to the non-linearities in the measurements, both for RSSI and for acceleration, Extended Kalman Filter was used to minimize errors. A discrete time model for the system was formulated as

$$\mathbf{X}_k = f(\mathbf{X}_{k-1}) + \mathbf{w}_\mathbf{k} \tag{1}$$

where  $\mathbf{X}_k$  is the state vector at the time k; the state transition function, f(.), was used to estimate the future state of the mobile node and  $\mathbf{w}_k \sim N(0, \mathbf{Q}_k)$  is a random variable that represented the noise with zero mean and covariance matrix  $\mathbf{Q}_k$ . Here,

$$f(\mathbf{X}_{k-1}) = \mathbf{A}_k \mathbf{X}_{k-1}$$

where

$$\mathbf{A}_{k} = \begin{bmatrix} 1 & 0 & dt & 0 & dt^{2}/2 & 0 \\ 0 & 1 & 0 & dt & 0 & dt^{2}/2 \\ 0 & 0 & 1 & 0 & dt & 0 \\ 0 & 0 & 0 & 1 & 0 & dt \\ 0 & 0 & 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 0 & 0 & 1 \end{bmatrix}.$$

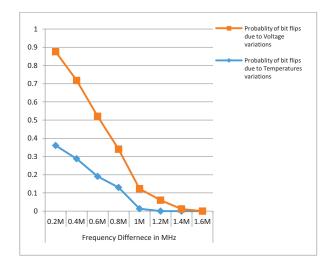

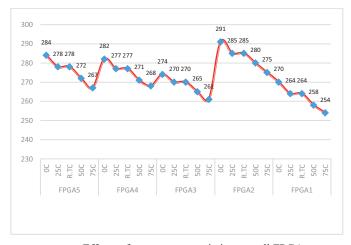

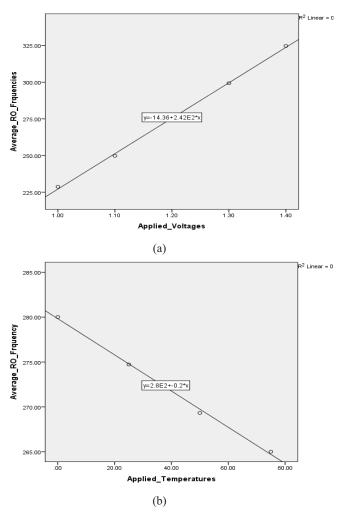

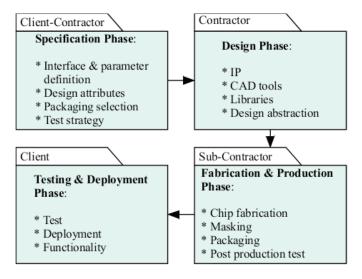

(2)