# **SESSION**

# MODELING, SIMULATION, AND RELATED ALGORITHMS + DATA STRUCTURES + OPERATING SYSTEMS

# Chair(s)

TBA

# On Modeling Inhibitor Nets with Interval Processes and Interval Traces

#### Mohammed Alqarni and Ryszard Janicki

Computing and Software Department, McMaster University, Hamilton, Ontario, Canada alqarnma@mcmaster.ca, janicki@mcmaster.ca

*Abstract*—Two interval semantics for elementary inhibitor Petri nets, interval process semantics and interval trace semantics are discussed and proved equivalent.

**Keywords:** inhibitor Petri nets, interval processes, interval traces, semantics

#### I. INTRODUCTION

It is commonly assumed (first argued by N. Wiener in 1914 [26] and analyzed in details in [10]) that any system run (execution) that can be observed by a single observer *must* be an interval order of event occurrences. This means that the most precise observational semantics is defined in terms of interval orders. Moreover, representing observations as interval orders allows to capture behaviours that neither of the standard semantics can really describe. However generating interval order directly is problematic for most models of concurrency, as the only feasible sequence representation of interval order is by using Fishburn Theorem [6] and appropriate sequences of *beginnings* and *endings* of events involved (cf. [10]).

Elementary nets with inhibitor arcs [11] are very simple. They are just classical elementary nets of [21], [24] extended with inhibitor arcs. However they can model extremely complicated behaviours [2], [4] that cannot easily (if not at all) be represented by other models. For example they can model the case when a simultaneous execution of events a and b and the order a followed by b are allowed, but the order b followed by a is forbidden, so called 'a not after b' case [9], [16]. This case cannot be represented by classical Place/Transition Nets [16]. Hence, the elementary nets with inhibitor arcs are an excellent medium for novel models of behaviours.

Interval process semantics of elementary inhibitor Petri nets has been proposed and analyzed in [3] and interval traces have been introduced in [12] and further developed in [13]. The interval processes of [3] are an extension and generalization of step-sequence process semantics of elementary inhibitor Petri nets proposed in [11] and improved in [15]; while the interval traces are a generalization of classical Mazurkiewicz traces [5], [18].

In this paper we introduce an interval traces semantics of elementary inhibitor Petri nets and show that this semantics is equivalent to the interval process semantics of [3].

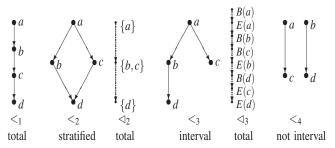

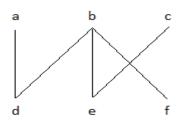

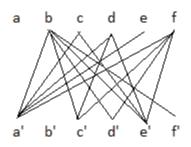

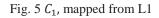

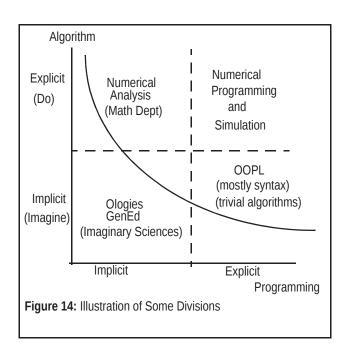

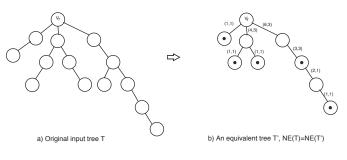

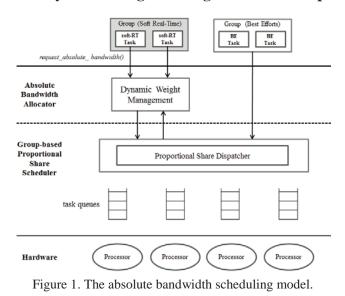

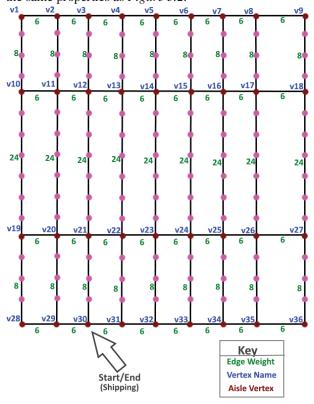

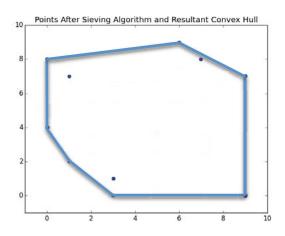

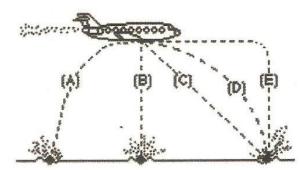

Figure 1: Various types of partial orders (represented as Hasse diagrams). The interval order  $<_3$  is (*not* uniquely) represented by a sequence that represents  $\lhd_3$ , i.e. B(a)E(a)B(b)B(c)E(b)B(d)E(c)E(d).

The process semantics as proposed in [3], i.e. in the style of [15], [21], does not usually require much validation as intuitively it is just a set of system unfoldings, so it is as natural as any operational semantics. Hence, the results of this paper can also be interpreted as a validation of the interval traces semantics.

#### II. PARTIAL ORDERS AND MAZURKIEWICZ TRACES

In this section, we recall some known mathematical concepts, notations and results that will be used frequently in this paper.

A relation  $R \in X \times X$  is an *equivalence relation*, if it is *reflexive, symmetric and transitive*, i.e. for all  $a,b,c \in X$ ,  $aRa, aRb \implies bRa$  and  $aRbRc \implies aRc$ .

If *R* is an equivalence relation than for every  $x \in X$ , the set  $[x]_R = \{y \mid xRy\}$  is the *equivalence class containing x*.

For every relation R, the relation  $R^* = \bigcup_{i=0}^{\infty} R^i$ , where  $R^0$  is the identity relation, is the *reflexive and transitive closure* of R.

**Definition 1.** A relation  $\leq \subseteq X \times X$  is a (strict) **partial order** if it is irreflexive and transitive, i.e. for all  $a, c, b \in X$ ,  $a \not\leq a$ and  $a < b < c \implies a < c$ . We also define:

$$\begin{array}{l} a \frown_{<} b & \stackrel{dg}{\longleftrightarrow} & \neg(a < b) \land \neg(b < a) \land a \neq b, \\ a < \frown b & \stackrel{df}{\longleftrightarrow} & a < b \lor a \frown_{<} b. \end{array}$$

*Note that a*  $\frown_{<} b$  *means a and b are* incomparable (*w.r.t.* <) *elements of X.*

Let < be a partial order on a set X. Then:

- < is *total* if ~\_<=Ø. In other words, for all a, b ∈ X, a < b ∨ b < a ∨ a = b. For clarity, we will reserve the symbol ⊲ to denote total orders;

- 2) < is *stratified* if  $a \frown_{<} b \frown_{<} c \Longrightarrow a \frown_{<} c \lor a = c$ , i.e., the relation  $\frown_{<} \cup id_X$ , where  $id_X$  is the identity on *X*, is an equivalence relation on *X*;

- 3) < is *interval* if for all  $a,b,c,d \in X$ ,  $a < c \land b < d \implies a < d \lor b < c$ , i.e., < has no restriction that is isomorphic to <<sub>4</sub> from Figure 4.

It is clear from these definitions that every total order is stratified and every stratified order is interval. The following simple concept will often be used in this paper.

For every partial order <, we define  $\mathsf{Total}(<) \stackrel{df}{=} \{ \lhd \subseteq X \times X \mid \lhd \text{ is a total order and } < \subseteq \lhd \}.$

In other words, the set Total(<) consists of all the *total* order extensions of <.

By Szpilrajn's Theorem [25], we know that every partial order < is uniquely represented by the set Total(<). Szpilrajn's Theorem can be stated as follows:

**Theorem 1** (Szpilrajn [25]). For every partial order

$$<$$

,

$<= \bigcap_{\lhd \in \mathsf{Total}(<)} \lhd$ .

For the interval orders, the name and intuition follow from Fishburn's Theorem:

**Theorem 2** (Fishburn [6]). A partial order < on X is interval *iff there exists a total order*  $\lhd on some T$  and two mappings  $B, E: X \rightarrow T$  such that for all  $x, y \in X$ ,

$$1. \ B(x) \triangleleft E(x) \qquad 2. \ x < y \iff E(x) \triangleleft B(y) \qquad \Box$$

Usually B(x) is interpreted as the beginning and E(x)as the end of an *interval* x. The intuition of Fishburn's theorem is illustrated in Figure 4 with  $<_3$  and  $\triangleleft_3$ . For all  $x, y \in \{a, b, c, d\}$ , we have  $B(x) \triangleleft_3 E(x)$  and  $x <_3 y \iff$  $E(x) \triangleleft_3 B(y)$ . For better readability in the future we will skip parentheses in B(x) and E(x), and just write Bx and Ex.

- **Definition 2** ([5], [17], [18]). 1) Let  $\Sigma$  be a finite set and let the relation ind  $\subseteq \Sigma \times \Sigma$  be an irreflexive and symmetric relation (called independency). The pair  $(\Sigma, ind)$  is called a trace alphabet.

- Let ≈∈ Σ\* × Σ\* be a relation defined as follows: x ≈ y ⇐⇒

$\exists x_1, x_2 \in \Sigma^*. \exists (a, b) \in ind. \ x = x_1 a b x_2 \land y = x_1 b a x_2$

- Let ≡<sub>ind</sub> the reflexive and symmetric closure of ≈, i.e. ≡<sub>ind</sub> = ≈\*. Clearly is an equivalence relation.

- 4) For every  $x \in \Sigma$ , the equivalence class  $[x]_{\equiv_{ins}}$  is called a Mazurkiewicz trace, or just a trace.  $\Box$

We will often write [x] or  $[x]_{ind}$  instead of  $[x]_{\equiv_{Ind}}$ .

One may show that  $[x][y] = [x] \circ [y] = [xy]$ , where  $\circ$  is a concatenation of sets of sequences, a symbol that is usually omitted [5], [18].

Formally, an algebra of Mazurkiewicz traces is a quotient equational monoid over sequences [5], [17], [18].

**Example 1.** Let  $\Sigma = \{a, b, c\}$ , ind =  $\{(b, c), (c, b)\}$ . Given three sequences s = abcbca,  $s_1 = abc$  and  $s_2 = bca$ , we can generate the traces  $[s] = \{abcbca, abccba, acbbca, acbcba, abbcca, accbba\}$ ,  $[s_1] = \{abc, acb\}$  and  $[s_2] = \{bca, cba\}$ . Note that  $[s] = [s_1][s_2]$  since [abcbca] = [abc][bca] = [abc bca].

Each sequence of events represents a total order of *enumerated events* in a natural way. For precise definitions see for example [11], here we will be using the following notation.

- 1) For each set of events  $\Sigma$ , let  $\widehat{\Sigma} = \{a^{(i)} \mid a \in \Sigma, i \ge 1\}$ .

- For each sequence s ∈ Σ\*, let ŝ ∈ Σ̂\* denote its enumerated representation. For example if s = abbaa then ŝ = a<sup>(1)</sup>b<sup>(1)</sup>b<sup>(2)</sup>a<sup>(2)</sup>a<sup>(3)</sup>.

- For each sequence s ∈ Σ\*, Σ̂s denotes the set of all enumerated events of s. For example Σ̂abbaa = {a<sup>(1)</sup>, a<sup>(2)</sup>, a<sup>(3)</sup>, b<sup>(1)</sup>, b<sup>(2)</sup>}.

- 4) For each trace [s], we define  $\widehat{\Sigma}_{[s]} = \widehat{\Sigma}_s$ .

- 5) For ever  $s \in \Sigma^*$ ,  $\triangleleft_s$  is a *total order* defined by the enumerated sequence  $\hat{s}$ . Fore example  $\triangleleft_{abbaa} = a^{(1)} \rightarrow b^{(1)} \rightarrow b^{(2)} \rightarrow a^{(2)} \rightarrow a^{(3)}$ .

**Definition 3** ([18]). For every trace [x], the partial order

$\sphericalangle_{[x]}^{trace} = \bigcap_{s \in [x]} \triangleleft_s$

is called the partial order generated by [x].

**Example 2.** For the trace  $[s] = \begin{bmatrix} abcbca \end{bmatrix}$  from Example 1, we have  $\widehat{\Sigma}_{[s]} = \{a^{(1)}, b^{(1)}, c^{(1)}, b^{(2)}, c^{(2)}, a^{(2)}\}$ . The partial order  $\ll_{[s]}^{trace}$  generated by [s] is depicted as Hasse diagram on the right.

#### III. INTERVAL TRACES

The interval traces, introduced in [12] and refined in [13], stem from Mazurkiewicz traces [17], [18] and Fishburn's representation of interval orders [6].

Let  $\Sigma$  be a finite set (of events), and let

$\mathscr{E}_{\Sigma} = \{ Ba \mid a \in \Sigma \} \cup \{ Ea \mid a \in \Sigma \},\$

be the set of all beginnings and ends of events in  $\Sigma$ . We will often just write  $\mathscr{E}$  instead of  $\mathscr{E}_{\Sigma}$ . Every sequence from  $x \in \mathscr{E}^*$  defines a total order to(x), however not every such total order can be interpreted as a representation of some interval order. or example *BaBcBb* represents no interval order.

Let  $\mathscr{D} \subseteq \mathscr{E}$  and let  $s \in \mathscr{D}^*$ . We standardly define the projection of *s* onto  $\mathscr{D}$  as:  $\pi_{\mathscr{D}}(\varepsilon) \stackrel{df}{=} \varepsilon$ , and

$$\pi_{\mathscr{D}}(s\alpha) \stackrel{df}{=} \begin{cases} \pi_{\mathscr{D}}(s)\alpha & \text{if } \alpha \in \mathscr{D}, \\ \pi_{\mathscr{D}}(s) & \text{if } \alpha \notin \mathscr{D}. \end{cases}$$

For example  $\pi_{\{Ba,Ea\}}(BbBaEbBaEaEc) = BaBaEa$  and  $\pi_{\{Ba,Ea,Bc,Ec\}}(BbBaEbBaEaEc) = BaBaEaEc$ .

We say that a string  $x \in \mathscr{E}^*$  is an *interval sequence* iff  $\forall Bt, Et \in \mathscr{E}^*$ .  $\pi_{\{Bt, Et\}}(x) \in (BtEt)^*$ .

We will write  $\mathsf{InSeq}(\mathscr{E}^*)$  to denote the set of all interval sequences of  $\mathscr{E}^*$ . For example  $BbBaEbBaEaEc \notin \mathsf{InSeq}(\mathscr{E}^*)$ , while  $BaBcBbEbEaEc \in \mathsf{InSeq}(\mathscr{E}^*)$ .

**Definition 4** ([12]). Let  $x \in \text{InSeq}(\mathscr{E}^*_{\Sigma})$ , and let  $\blacktriangleleft_x$  be a relation on  $\widehat{\Sigma}$ , defined by

$a^{(i)} \blacktriangleleft_x b^{(j)} \iff Ea^{(i)} \triangleleft_x Bb^{(j)}.$

By Theorem 2, the relation  $\blacktriangleleft_x$  is an interval order, and it is called the interval order defined by the sequence x of beginnings and ends.

For example if x = BaEaBbBcEbBdEcEd then  $\blacktriangleleft_x$  is the interval order  $<_3$  from Figure 1.

**Definition 5** ([12]). Let ind  $\subseteq \mathscr{E} \times \mathscr{E}$  be a symmetric and irreflexive relation such that for all  $a, b \in \Sigma$

- 1)  $(Ba, Ea) \notin ind and (Ea, Ba) \notin ind$ ,

- 2)  $(Ba, Bb) \in ind and (Ea, Eb) \in ind.$

The relation ind is called interval independency, and the pair  $(\mathcal{E}, ind)$  is called interval trace alphabet.  $\Box$

The condition (1) above follows from the fact that in any representation of any order, the beginning of an event always precede the end so that cannot commute. The condition (2) follows from the generalization of the observation that the interval sequences *BaBbEaEb*, *BbBaEaEb*, *BaBbEbEa*, and *BbBaEbEa* represent the same fact, namely that *a* and *b* are simultaneous.

The interval traces are defined as a special distinctive class Mazurkiewicz traces.

**Definition 6** ([12]). A trace  $[x]_{ind}$  over the interval trace alphabet  $(\mathcal{E}, ind)$  is called an interval trace if  $[x]_{ind} \subseteq$ InSeq $(\mathcal{E}^*)$ .

The soundness of the above definition follows from the following non-trivial result.

**Proposition 1** ([13]). Let  $(\mathcal{E}, ind)$  be an interval trace alphabet, and let  $x, y \in \mathsf{InSeq}(\mathcal{E}^*)$ .

- 1) For each  $x, y \in \mathscr{E}^*$ , if  $x \in \mathsf{InSeq}(\mathscr{E}^*)$  and  $y \in \mathsf{InSeq}(\mathscr{E}^*)$ then  $xy \in \mathsf{InSeq}(\mathscr{E}^*)$ .

- For each s ∈ E\*, we have: s ∈ lnSeq(E\*) ⇔ ∀x ∈ [s]<sub>ind</sub>. x ∈ lnSeq(E\*).

For each x, y ∈ E\*, if [x]<sub>ind</sub> ⊆ lnSeq(E\*) and [y]<sub>ind</sub> ⊆ lnSeq(E\*), then [x]<sub>ind</sub>[y]<sub>ind</sub> = [xy]<sub>ind</sub> ⊆ lnSeq(E\*).

$$\begin{array}{l} x = x \\ x = 4 \\ y \end{array} \xrightarrow{[X] ind} y \\ x \equiv ind \\ y. \end{array}$$

As a partial orders generator, each interval trace can be interpreted twofold. First, it is also a Mazurkiewicz trace so it generates a partial order by Definition 3, second, each element of the interval trace is an interval sequence, so the trace can also be interpreted as representing a set of appropriate interval orders. **Definition 7.** Let  $[x] \subseteq \mathsf{InSeq}(\mathscr{E}^*)$  be an interval trace.

Both the canonical order and the interval orders defined by an interval trace will be used to show the equivalence of interval order semantics and interval process semantics for elementary inhibitor nets.

#### IV. ELEMENTARY NETS WITH INHIBITOR ARCS

Inhibitor arcs allow a transition to check for an *absence* of a token. They have been introduced in [2] to solve a synchronization problem not expressible in classical Petri nets. In principle they allow 'test for zero', an operator the standard Petri nets do not have (c.f. [20], [23]). Activator arcs (also called 'read', or 'contextual' arcs [4], [19]), formally introduced in [11], [19], are conceptually orthogonal to the inhibitor arcs, they allow a transition to check for a *presence* of a token.

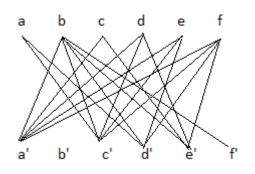

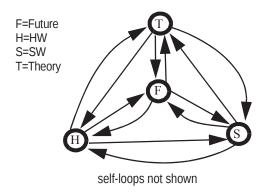

*Elementary nets with inhibitor arcs* [11] are very simple. They are just classical *elementary nets* of [21], [24] extended with inhibitor arcs. Nevertheless they can easily express complex behaviours involving 'not later than' cases or nontransitive simultaneity as illustrated in Figure 2.

**Definition 8** ([2], [11]). An Elementary Net with Inhibitor Arcs (ENI) is a tuple  $\mathbb{N} = (P, T, F, C_{init}, I)$  such that

- *P* and *T* are finite and disjoint sets of places and transitions represented, respectively, as circles and rectangles;

- *F* ⊆ (*P*×*T*) ∪ (*T*×*P*) is the flow relation of N represented as directed arcs between places and transitions;

- *C*<sub>init</sub> ⊆ *P* is the initial marking of N (generally, any C ⊆ *P* is a marking); and

- $I \subseteq P \times T$  is a set of inhibitor arcs represented as arcs with small circles as arrowheads.

The net N in Figure 2 is an example of ENI. For every  $x \in P \cup T$  we define, its input  ${}^{\bullet}x = \{y \mid (y,x) \in F\}$  and its output  $x^{\bullet} = \{y \mid (x,y) \in F\}$ . We assume that for every  $t \in T$ ,  ${}^{\bullet}t \neq \emptyset \neq t^{\bullet}$  and  ${}^{\bullet}t \cap t^{\bullet} = \emptyset$ . Moreover, for each  $t \in T$ , the set  ${}^{\circ}t = \{p \mid (p,t) \in I\}$  is the set of places that are connected with transition *t* by inhibitor arcs. We also standardly define for any subset *U* of *T*:  ${}^{\bullet}U = \bigcup_{t \in U} {}^{\bullet}t$ ,  $U^{\bullet} = \bigcup_{t \in U} t^{\bullet}$  and  ${}^{\circ}U = \bigcup_{t \in U} {}^{\circ}t$ .

The operational semantics of ENI is defined through the "token game" which simulates the occurrence of transitions and the changes of tokens in places. ENI differs from ordinary elementary Petri nets only by introducing a requirement that a transition cannot be enabled if there is a token in a place to which it is connected by an

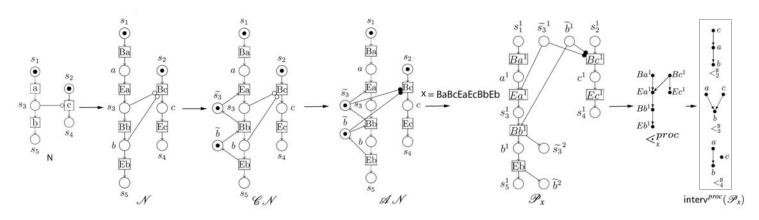

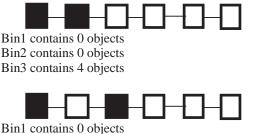

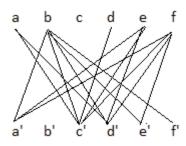

Figure 2: Inhibitor nets N and N<sub>io</sub> and all their behaviours involving one occurrence of *a*, *b* and *c*. The net N generates  $<_{1}^{N}, <_{2}^{N}, <_{3}^{N}, <_{4}^{N}$ , and two concurrent histories, while N<sub>io</sub> generates only an interval order  $<_{4}^{N}$ . Partial orders are represented by Hasse diagrams. The net N<sub>io</sub> generates only the interval order  $<_{4}^{N}$ .

inhibitor arc. A transition *t* is enabled at a configuration *C* if  ${}^{\bullet}t \subseteq C$  and  $(t^{\bullet} \cup t^{\circ}) \cap C = \emptyset$ . An enabled transition *t* can fire leading to a new configuration  $C' = (C \setminus {}^{\bullet}t) \cup t^{\bullet}$ . We denote this by  $C[t\rangle C'$ . We will also write  $C[t_1 \dots t_n\rangle C'$  if  $C[t_1\rangle C_1 \dots C_{n-1}[t_n\rangle C'$  for some configurations  $C_1, \dots, C_{n-1}$ .

There are two standard operational semantics for ENI, one in terms of **firing sequences** and another in terms of **firing step sequences** (c.f. [11]), however in this paper we will only use the firing sequenc semantics.

**Definition 9.** A firing sequence of an ENI is any sequence of transitions  $t_1, \ldots, t_n$  for which there are markings  $C_1, \ldots, C_n$  satisfying:

$$C_{init}[t_1\rangle C_1[t_2\rangle C_2\dots[t_n\rangle C_n.$$

#### V. INTERVAL ELEMENTARY NET WITH INHIBITOR ARCS

Following [3] in this section we show how a given inhibitor net can generate appropriate sequences of event beginnings and ends, so we will be able to describe all interval orders the net generates.

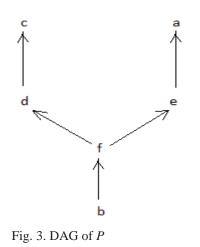

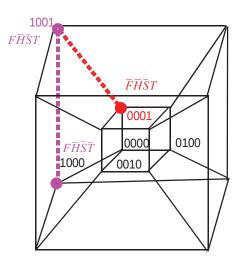

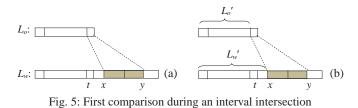

The basic idea of defining the set of firing interval sequences for a given inhibitor net N is briefly presented in Figure 3 as a transformation of N into  $\mathcal{N}$ .

We assume that the events (transitions) are not instantaneous, on contrary, they are interpreted as representations of activities whose completion takes some time. However, their beginnings and ends are instantaneous.

In principle the transformation is based on the replacement of a transition t by the net  $Bt \rightarrow t \rightarrow Et$  as first proposed in [27] and additionally taking into account specific behaviours induced by inhibitor arcs.

**Definition 10** ([3]). Let  $N = (P,T,F,I,C_{init})$  be an ENI system. We define  $\mathcal{N} = (\mathcal{P}, \mathcal{T}, \mathcal{F}, \mathcal{I}, C_{init})$ , its interval representation as follows:

•

$$\mathscr{P} = P \cup T$$

- $\mathscr{T} = \{Bt \mid t \in T\} \cup \{Et \mid t \in T\}$

- $\forall p \in P, t \in T. (p,t) \in F \iff (p,Bt) \in \mathscr{F}$

•

$$\forall p \in P, t \in T. (t,p) \in F \iff (Et,p) \in \mathscr{F}$$

•

$$\forall t \in I$$

.  $(Bl, t), (t, El) \in \mathscr{P}$

•  $\forall p \in P, t \in T$ .  $(p,t) \in I \iff$

$(p,Bt) \in \mathscr{I} \land (\forall r \in p^{\bullet})(r,Bt) \in \mathscr{I}$ .  $\Box$

For the detailed arguments that the net  $\mathcal{N}$  fully describes the behaviour of the net N the reader is referred to [3].

The nets N and  $\mathcal{N}$  in Figure 3 illustrate the above definition. Note that for example each of the following sequences BaBcEaBbEbEc, BaBcEaBbEcEb, BcBaEaBbEbEc and BcBaEaBbEcEb are firing sequences of  $\mathcal{N}$ , and each of them represents the *interval order*  $<_4^{\mathbb{N}}$  from Figure 2 via Fishburn Theorem (Theorem 2). This means that event b follows event a and event c overlaps both events a and b in the original net N.

Directly from the above definition we have:

**Fact 1** ([3]). Let  $N = (P, T, F, I, C_{init})$  be an ENI system and  $\mathcal{N} = (\mathcal{P}, \mathcal{T}, \mathcal{F}, \mathcal{I}, C_{init})$  its interval representation. Then for each  $t \in T$  we have:  ${}^{\bullet}Bt = {}^{\bullet}t$ ,  $Bt^{\bullet} = \{t\}$ ,  ${}^{\bullet}Et = \{t\}$ ,  $Et^{\bullet} = t^{\bullet}$ ,  $Bt^{\circ} = t^{\circ} \cup (t^{\circ})^{\bullet}$ , and  $Et^{\circ} = \emptyset$ .

Since  $\mathscr{N}$  is just another inhibitor net, we may try to use the standard definition of a firing sequence from Definition 9. We will write  $[\ldots\rangle$  instead of  $[\cdots\rangle$  to indicate firing in  $\mathscr{N}$  (or  $\mathscr{C}\mathscr{N}$ ) and not in N.

**Definition 11** ([3]). Let  $\mathcal{N} = (\mathcal{P}, \mathcal{T}, \mathcal{F}, \mathcal{I}, C_{init})$  be an interval ENI. A sequence  $x = \alpha_1 \dots \alpha_n \in \mathcal{T}^*$  is an interval firing sequence of  $\mathcal{N}$  if there are markings  $C_1, \dots, C_n$  satisfying:

$$C_{init} [[t_1]\rangle C_1 [[t_2]\rangle C_2 \dots [[t_n]\rangle C_n. \square$$

The following result validates the above definition.

**Proposition 2** ([3]). If x is an interval firing sequence of  $\mathcal{N}$ , then  $x \in \mathsf{InSeq}(\mathcal{T}^*)$ .

Since all transitions of interval ENI's are instantaneous, simultaneous executions of any kind are are disallowed, so the only operational semantics is the firing sequences semantics. The firing step sequences, as in [11], [15] do not make any sense in this case.

The net  $\mathcal{N}$  from Figure 3 have ten interval firing sequences that involve all elements of  $\mathscr{T} = \{Ba, Ea, Bb, Eb, Bc, Ec\}, \text{ namely } BaEaBbEbBcEc$ - which represents a total order  $<_{1}^{\mathbb{N}}$  from Figure 2; BcEcBaEaBbEb - which represents a total order  $<_{2}^{\mathbb{N}}$ ; BaBcEcEaBbEb, BaBcEaEcBbEb, BcBaEcEaBbEb, BcBaEaEcBbEb - all four represent a stratified order  $<_{3}^{\mathbb{N}}$  of Figure 2; and *BaBcEaBbEbEc*, *BaBcEaBbEcEb*, BcBaEaBbEbEc, BcBaEaBbEcEb - all four represent an interval order  $<_4^{\mathbb{N}}$  of Figure 2. It is important to stress that if observations are not allowed to be recorded as interval firing sequences, then  $<_4^{\mathbb{N}}$  cannot be generated. It can neither be generated by firing sequence nor by firing step-sequence. This order is an interval order, but it is not stratified, so

Figure 3: An example of an inhibitor net, its interval representation, a process and a concurrent histories it generates.

step-sequences (as in [11], [15]) do not work.

It was shown in [3] that if all interval orders generated by a net are stratified then observational semantics of this model is equivalent to that of [11], [15].

The net  $N_{io}$  from Figure 2 can generate neither any firing sequence nor any step-sequence. It can generate only the interval order  $<_4^N$  (see [3], [13] for details).

#### VI. PROCESS SEMANTICS

In case of concurrent systems many of system runs/executions are equivalent, but this aspect is difficult to capture when only operational semantics is considered. Abstractions of these equivalent executions are often called *concurrent histories*, and, dependently on the assumptions about systems and systems runs, are usually modelled by partial orders [7], [21], stratified order structures or interval order structures (c.f. [8]), or *processes* (c.f. [15]).

For the net N from Figure 2, the runs  $<_2^N, <_3^N, <_4^N$  are equivalent as in all cases we have event *c* occurs no later than event *a*, so N has two concurrent histories involving all three events *a*, *b*, *c*. In  $<_1^N$ , *a* and *b* occur before *c*, so  $<_1^N$  belongs to a different concurrent history<sup>1</sup> (see [8], [9] for details).

For Petri nets, *processes* are plain or modified unfoldings, called *occurrence nets*. It was shown in [11], [15] that for nets *with* inhibitors arcs, plain unfolding does not work, since the absence of a token, unlike the presence of a token, cannot be tested. Hence we have to replace inhibitor arcs by appropriate activator arcs. The idea is that an *inhibitor arc* which tests whether a place is empty, can be simulated by an *activator arc* which tests whether its *complement place* is not empty. To do such simulation, each inhibitor place must have its complements, if it does not we can always add it, as it does not change the net behaviour (c.f. [7], [11], [15], [21]). This construction is illustrated in Figure 3, where adding complement places changes  $\mathcal{N}$  into  $\mathcal{CN}$ . Clearly

the behaviours of  $\mathcal{N}$  and  $\mathcal{CN}$  are identical (c.f. [11], [15], [21] for details).

- **Definition 12** ([7], [15]). 1) *Places*  $p, q \in P$  are complementary (p is a complement of q and vice versa) if  $p \neq q$ ,  $\bullet p = q \bullet$  and  $p \bullet = \bullet q$ , and  $|C_{init} \cap \{p,q\}| = 1$ .

- 2) An elementary inhibitor net is complement closed if every inhibitor place has its complement, i.e. (p,t) ∈ I ⇒ p̃ ∈ P.

If p and q are complementary we will write  $p = \tilde{q}, q = \tilde{p}$ , and clearly  $p = \tilde{p}, q = \tilde{q}$ .

We define the processes generated by a firing sequence  $y = t_1 \dots t_n$  as  $P_y = N_n$ , where  $N_n$  is the last activator occurrence net in the sequence  $N_0, \dots, N_n$ . Each net  $N_k = (B_k, E_k, R_k, A_k), 0 \le k \le n$ , is a net with activator arcs that model an unfolding of the net N by the sequence  $t_1 \dots t_k$ . The first three components of  $N_k$  correspond to places P, transitions T, and flow relation F of the underlying ENI system, while  $A_k \subseteq B_k \times E_k$  is the set of activator arcs derived from inhibitors arcs I.

The elements of  $B_k \cup E_k$  are of the form  $r^i$ , where  $r \in P \cup T$ and  $i \ge 1$ . We will denote  $l(r^i) = r$  and  $n(r^i) = i$ . Moreover, for every  $r \in P \cup T$  and  $k \le n$ ,  $\Delta r$  is the number of nodes of  $N_{k-1}$  labelled by r (i.e. the number of  $\alpha \in B_k \cup E_k$  such that  $l(\alpha) = r$ .)

**Algorithm 1** (Constructing  $P_y$ , for  $y = t_1 ... t_n$ , [11], [15]).

- Step 0.  $N_0 = (\{(p^1) \mid p \in C_{init}\}, \emptyset, \emptyset, \emptyset)$

- Step k. Given  $N_{k-1}$ , we define  $N_k$  in the following way:

$$\begin{array}{l} - & B_{k} = B_{k-1} \cup \{p^{1+\Delta p} \mid p \in t_{k}^{\bullet}\} \\ - & E_{k} = E_{k-1} \cup \{t_{k}^{1+\Delta t_{k}}\} \\ - & R_{k} = R_{k-1} \cup \{(p^{\Delta p}, t_{k}^{1+\Delta t_{k}}) \mid p \in ^{\bullet}t_{k}\} \\ & \cup \{(t_{k}^{1+\Delta t_{k}}, p^{1+\Delta p}) \mid p \in t_{k}^{\bullet}\} \\ - & A_{k} = A_{k-1} \cup \{(\widetilde{p}^{\Delta \widetilde{p}}, t_{k}^{1+\Delta t_{k}}) \mid p \in t_{k}^{\circ}\} \end{array}$$

The above algorithm is illustrated in Figure 3 (a part from  $\mathscr{CN}$  to  $\mathscr{P}_x$ ). When it is applied to the net  $\mathscr{CN}$  with the sequence x = BaBcEaEcBaBb it results in the process  $\mathscr{P}_x$ . Intuitively it is just a plain unfolding of the net  $\mathscr{AN}$ .

<sup>&</sup>lt;sup>1</sup>Concurrent history is a set of runs that agree on causality invariants as "always earlier than" or "always not later than" (see [8], [9] for formal arguments).

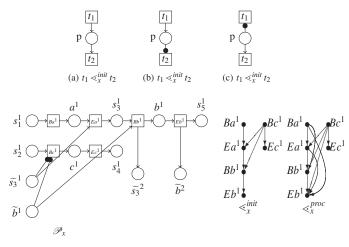

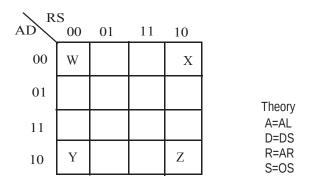

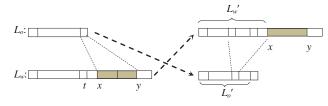

Figure 4: An illustration of Definition 13(1) (top) and Definition 13(2) (bottom).

An extension of Algorithm 1 to the case of firing step sequence  $x = U_1 \dots U_n$  was first proposed in [11]) and refined in [15] is rather straightforward, but in will not be discussed here as it will not be used.

Algorithm 1 can be applied to *any* elementary net with inhibitor arcs, however in this paper we will use it only to *complement closed interval representations*, as  $\mathscr{CN}$  in Figure 3.

#### VII. INTERVAL PROCESSES

We will now introduce interval processes and show how they represents interval runs/executions.

Let  $\mathbb{N} = (P, T, F, I, C_{init})$  be an ENI system,  $\mathcal{CN} = (\mathcal{P}, \mathcal{T}, \mathcal{F}, \mathcal{I}, C_{init})$  be its complement closed interval representation and let  $x = \alpha_1 \dots \alpha_n$  be an interval firing sequence of  $\mathcal{CN}$ .

Assume that Algorithm 1 applied to  $\mathscr{CN}$  with  $x = \alpha_1 \dots \alpha_n$  produced a process (an occurrence net)  $P_x$ .

Assume that  $P_x = \mathcal{N}_n = (\mathcal{B}_n, \mathcal{E}_n, \mathcal{A}_n, \mathcal{A}_n)$ , where  $\mathcal{N}_n$  is the last step of Algorithm 1.

A partial order  $\leq_x^{proc}$  derived from the process  $\mathscr{P}_x$  is defined as follows.

**Definition 13** ([15]). Let  $\mathscr{P}_x = \mathscr{N}_n = (\mathscr{B}_n, \mathscr{E}_n, \mathscr{R}_n, \mathscr{A}_n)$  be the process generated by *x*. We define a canonical partial order  $\lessdot_x^{proc}$  on  $\mathscr{E}_n$  as follows:

The above construction is illustrated in Figure 4. In most cases many different *x*'s can generate the same process  $\mathscr{P}_x$ , but the canonical partial order  $<_x^{proc}$  captures all the cases.

**Proposition 3** ([3]). For each interval firing sequence x,

$$\operatorname{total}(\triangleleft_x^{proc}) = \{ \triangleleft_y \mid \mathscr{P}_x = \mathscr{P}_y \}.$$

We will now define formally interval orders and interval order structures generated by interval firing sequences of  $\mathcal{N}$ .

**Definition 14.** Define  $E_n = \{t \mid Bt \in \mathscr{E}_n \land Et \in \mathscr{E}_n\}$ . Let  $x \in$ InSeq $(\mathscr{T}^*)$ , and let  $\blacktriangleleft_x$  be a relation on  $E_n$ , defined by  $a^i \blacktriangleleft_x b^i \iff Ea^i \triangleleft_x Bb^j$ .

By Theorem 2 the relation  $\blacktriangleleft_x$  is an interval order.  $\Box$

Each  $\mathscr{P}_x$  is generated from  $\mathscr{N}$  by an interval sequence x and each interval sequence x defines an interval order  $\blacktriangleleft_x$ . The set of all interval orders that can be derived from  $\mathscr{P}_x$  or  $\ll_x^{proc}$  is defined as follows.

**Definition 15.** For each interval firing sequence x, we define  $\operatorname{interv}^{ord}(\triangleleft_x^{proc}) = \operatorname{interv}^{proc}(\mathscr{P}_x) = \{\blacktriangleleft_y | \mathscr{P}_x = \mathscr{P}_y\}. \square$

For the example from Figure 3,  $interv^{ord}(\leq_x^{proc}) = interv^{proc}(\mathscr{P}_x) = \{<_2^N, <_3^N, <_4^N\}$ , i.e. the concurrent history  $hist_2^N$  from Figure 2. We will show that the same result is obtained when the interval traces approach is used.

VIII. INTERVAL TRACE SEMANTICS OF INHIBITOR NETS

Let  $\mathbb{N} = (P, T, F, I, C_{init})$  be an ENI system and let  $\mathcal{CN} = (\mathcal{P}, \mathcal{T}, \mathcal{F}, \mathcal{I}, C_{init})$  be its *complement closed interval representation*.

We define the *interval trace independency* relation  $ind_{\mathscr{C},\mathscr{N}} \subseteq \mathscr{T} \times \mathscr{T}$  as follows.

**Definition 16.** *For all distinct*  $a, b \in T$ *:*

1)

$$(Ba, Bb) \in ind_{\mathscr{CN}} \land (Ea, Eb) \in ind_{\mathscr{CN}}$$

2)  $(Ba, Eb) \in ind_{\mathscr{CN}} \iff$

$[(Ba^{\bullet} \cup {}^{\bullet}Ba) \cap (Eb^{\bullet} \cup {}^{\bullet}Eb) = \emptyset] \land$

$[(Ba^{\circ} \cap {}^{\bullet}Eb) \cup (Eb^{\circ} \cap {}^{\bullet}Ba) = \emptyset] \land$

$[(Ba^{\bullet} \cap Eb^{\circ}) \cup (Eb^{\bullet} \cap Ba^{\circ}) = \emptyset].$

The interval trace alphabet is  $(\mathcal{T}, ind_{\mathcal{CN}})$ .

The relation  $ind_{\mathscr{CN}}$  is a refinement of the similar relations from [11], [15].

**Definition 17.** Let  $x = \alpha_1 \dots \alpha_n$  be an interval firing sequence of CN. The interval trace  $[x]_{ind_{CN}}$  is the interval trace of CN generated by x.

Proposition 2 and the result below prove the soundness of the above definition.

**Proposition 4.** If x is an interval firing sequence of  $C \mathcal{N}$ ,  $C_{init}[[x] C_n$  for some n, and  $y \in [x]_{ind_{G,\mathcal{N}}}$ , then  $C_{init}[[y] C_n$ .

*Proof.* (sketch) It suffices to show it for |x| = 1, which can be derived from the definition of  $[\ldots]$ .

For the net  $\mathscr{CN}$  of Figure 3 and x = BaBcEaEcBbEb, the content of  $[x]_{ind_{\mathscr{CN}}}$  consists of ten sequences analyzed at the end of Section V and  $<_{[x]}^{trace}$  is the same as  $<_x^{proc}$ from Figures 3 and 4. Moreover interv<sup>trace</sup>( $[x]_{ind_{\mathscr{CN}}} =$ interv<sup>ord</sup>( $<_x^{proc}$ ) = interv<sup>proc</sup>( $\mathscr{P}_x$ ) = { $<_2^N, <_3^N, <_4^N$ }.

We will show this kind of relationship holds in all cases.

#### IX. INTERVAL PROCESSES VS INTERVAL TRACES

We start with the formal statement of the main theoretical result of this paper.

**Theorem 3** (Equivalence of Process and Interval Traces Semantics). Let  $\mathbb{N} = (P,T,F,I,C_{init})$  be an ENI system,  $\mathscr{CN} = (\mathscr{P}, \mathscr{T}, \mathscr{F}, \mathscr{I}, C_{init})$  be its complement closed interval representation and let  $x = \alpha_1 \dots \alpha_n$  be an interval firing sequence of  $\mathscr{CN}$ . The the following equations hold:

1)

$$\leq_{[x]_{ind_{\mathscr{C}},\mathscr{N}}}^{trace} = \leq_{x}^{proc}$$

2) interv<sup>trace</sup> $([x]_{ind_{\mathscr{C}},\mathscr{N}}) = interv^{ord}(\leq_{x}^{proc}) = interv^{proc}(\mathscr{P}_{x})$

*Proof.* (idea.) First note that due to Proposition 3, it is relatively easy to show that  $(1)\Rightarrow(2)$ , so proving (1) is enough. The proof of (1) is by induction on the length of *x*. The proof is long, tedious, non-trivial, and plenty of different cases have to be considered.

The above theorem is an equivalent of similar seminal results for step sequences (i.e. stratified orders) operational semantics, comtraces and stratified orders process semantics of [11], [15]. In principle it states that the in interval process semantics and interval traces semantics are equivalent for elementary inhibitor nets.

#### X. FINAL COMMENT

This paper deals with the case when all observations/system runs are represented by interval orders. This is often regarded as a the most general case [10], [26]. We concentrated on elementary inhibitor Petri nets, applied the interval traces semantics of [12], [13] to these kind of nets, and showed that in this case the interval process semantics proposed in [3] and the interval traces semantics are equivalent. The results of this paper can be interpreted as an extension of the ideas of [11], [15] to interval order observations.

Since the process type semantics, which is based on the concept of system unfolding, is very natural and usually does not require justification, the results of this paper can also be interpreted as some validation of the interval order semantics for inhibitor nets.

Usually the concurrent histories involving interval or stratified orders and "not later than" phenomenon are represented by interval or stratified order structures (c.f. [3], [8], [11], [12], [13], [15] and others). For our case the interval order structures would be relevant. However this notion has not been used in this paper. The main result of [1] show that the canonical orders like  $\leq_x^{proc}$  and  $\leq_{[x]}^{trace}$  uniquely represent appropriate interval order structures, so we do not have to use them explicitly.

An extension to general Place/Transition nets (as [14] did to some aspects of the model of [11], [15]) is a serious future research project.

#### ACKNOWLEDGMENTS

Mohammed Alqarni acknowledges the full support by Ministry of Education in Saudi Arabia through The Saudi Arabian Cultural Bureau in Canada, and Ryszard Janicki acknowledges the partial support by NSERC grant of Canada.

#### REFERENCES

- Abraham, U., Ben-David, S., Magidor, M.: On global-time and interprocess communication. In Semantics for Concurrency, Workshops in Computing, pp. 311–323, Springer (1990)

- [2] Agerwala, T., Flynn, M.: Comments on capabilities, limitations and "correctness" of Petri nets, *Computer Architecture News* 4 (2), 81-86 (1973).

- [3] Alqarni, M., Janicki, R.: On Interval Process Semantics of Petri Nets with Inhibitor Arcs, Proc. of ICATPN'2015, *Lecture Notes in Computer Science*, 2015, to appear

- [4] Baldan, P., Busi, N., Corradini, A., and Pinna, G. M.: Domain and event structure semantics for Petri nets with read and inhibitor arcs, *Theoretical Computer Science* 323, 129-189 (2004)

- [5] Diekert V., Rozenberg, G. (eds.): *The Book of Traces*. World Scientific, Singapore (1995)

- [6] Fishburn, P. C.: Intransitive indifference with unequal indifference intervals. *Journal of Mathematical Psychology* 7, 144–149 (1970).

- [7] Goltz, U. and Reisig, W.: The non-sequential behaviour of Petri nets. Information and Control, 57(2):125–147, 1983.

- [8] Janicki, R.: Relational Structures Model of Concurrency. Acta Informatica 45, 279–320 (2008)

- [9] Janicki, R., Kleijn, J., Koutny, M.: Quotient Monoids and Concurrent Behaviours. In Martin-Vide, C. (ed.), Scientific Applications of Language Methods, pp. 311-385, Imperial College Press, London (2010)

- [10] Janicki, R., Koutny, M.: Structure of Concurrency. *Theoretical Computer Science* 112, 5–52 (1993)

- [11] Janicki, R., Koutny, M.: Semantics of Inhibitor Nets. Information and Computation 123(1), 1–16 (1995)

- [12] Janicki, R., Yin, X., Zubkova, N.: Modeling Interval Order Structures with Partially Commutative Monoids. In Proc. of CONCUR'2012, *Lecture Notes in Computer Science*, vol. 7454, pp. 425-439 (2012)

- [13] Janicki, R., Yin, X.: Modeling Concurrency with Interval Orders, Information and Computation, submitted

- [14] Juhás, G., Lorenz, R., Mauser, S.: Complete Process Semantics for Inhibitor Nets, Proc. of ICATPN'2007 Lecture Notes in Computer Science, vol. 4546, pp 184-203 (2007)

- [15] Kleijn, J., Koutny, M.: Process Semantics of General Inhibitor Nets. Information and Computation 190, 18–69 (2004)

- [16] Kleijn, J., Koutny, M.: Formal Languages and Concurrent Behaviour. Studies in Computational Intelligence 113, 125–182 (2008).

- [17] Mazurkiewicz, A.: Concurrent Program Schemes and Their Interpretation. TR DAIMI PB-78, Comp. Science Depart., Aarhus University (1977)

- [18] Mazurkiewicz, A.: Introduction to Trace Theory. In [5], pp. 3-42.

- [19] Montanari, U., Rossi, F.: Contextual nets, Acta Informatica 32 (6), 545–596 (1995).

- [20] Murata T.: Petri nets: Properties, analysis and applications, Proc. of IEEE 77 (4), 541-579 (1989)

- [21] Nielsen, M., Rozenberg, G., Thiagarajan, P. S.: Behavioural Notions for Elementary Net Systems. *Distributed Computing* 4, 45–57 (1990)

- [22] Ochmański, E., Recognizable Trace Languages, in [5], pp. 167-204. [23] Peterson, J. L.: *Petri nets theory and the modelling of systems*,

- Prentice-Hall, 1981

[24] Rozenberg, G. Engelfriet, J.: Elementary Net Systems, in Lectures on Petri Nets I: Basic models, *Lecture Notes in Computer Science*, vol 1492, pp. 12–121 (1998)

- [25] Szpilrajn, E.: Sur l'extension de l'ordre partiel. Fundam. Mathematicae 16, 386–389 (1930)

- [26] Wiener, N.: A contribution to the theory of relative position, Proc. of the Cambridge Philosophical Society 17, 441–449 (1914)

- [27] Zuberek, W. M.: Timed Petri nets and preliminary performance evaluation. In Proc. of the 7-th Annual Symp. on Computer Architecture, pp. 89–96, La Baule, France (1980)

# Data Structures and Algorithms for Partitioning a Set into Sets of non-Descending Cardinality

Oshani Titti, Yijie Han School of Computing and Engineering University of Missouri at Kansas City Kansas City, MO 64110

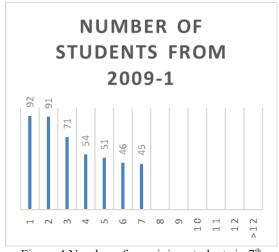

Abstract- Data structures have been around since the structured programming era. Algorithms often associate with data structures. An algorithm is a sequence of instructions that accomplishes a task in a finite time period. The algorithm receives zero or more inputs, produces at least one output, consists of clear and unambiguous instructions, terminates after a finite number of steps, and is basic enough that a person can carry out the algorithm using a pencil and paper. Algorithms for dividing objects into bins have long been invented. However, dividing objects in summation format is not received due attention. In this paper, objects are divided into n bins in such a way that the next bin will contain more than or equal number of objects than the preceding bin.

Keywords: Data structure, algorithms, edge partition, integer partition, non-descending order partition.

### 1. Introduction

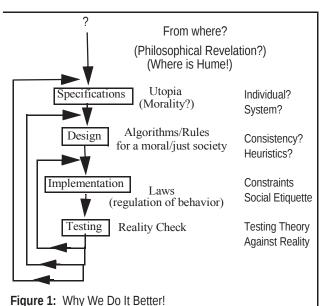

Computer science is often difficult to define. This is probably due to the unfortunate use of the word "computer" in the name. As you are perhaps aware, computer science is not simply the study of computers. Although computers play an important supporting role as a tool in the discipline, they are just that-tools.

Computer science is the study of problems, problemsolving, and the solutions that come out of the problemsolving process. Given a problem, a computer scientist's goal is to develop an **algorithm**, a step-by-step list of instructions for solving any instance of the problem that might arise. Algorithms are finite processes that if followed will solve the problem. Algorithms are solutions.

Computer science emphasizes two important topics: data structures and algorithms. Those topics are important because the choices you make for a program's data structures and algorithms affect that program's memory usage

(for data structures) and CPU time (for algorithms that interact with those data structures).

This paper initiates a two-part series that explores data structures and algorithms. When choosing a data structure or algorithm, you sometimes discover an inverse relationship between memory usage and CPU time: the less memory a data structure uses, the more CPU time associated algorithms need to process the data structure's *data items*, which are primitive type values or objects, via references. Also, the more memory a data structure uses, the less CPU time associated algorithms need to process the data items—and faster algorithms result. This paper begins with a presentation of basic concepts and continues with a tour of the array data structure.

## 2. Approach

Consider 'm' objects which have to be divided into 'n' bins in such a way that the next bin should not contain less objects than the previous bin. Suppose first bin contains 1 object then all other bins should contain at least 1 object. Similarly if the fourth bin contains 3 objects then all other bins after fourth bin should contain a minimum of 3 objects. This is the method of dividing objects in the form of steps into the bins.

The number of ways of dividing m objects in n bins is represented as f(m, n).

The number of objects that are being divided into the bins will remain same or in increasing order which is in the form of steps but never decreases.

### 3. Method

Let there be 'm' distinct objects say 10, 20, 30, 40.....mo and 'n' distinct bins say 1b, 2b, 3b.....nb. Let the function of dividing 'm' objects into 'n' bins be f(m, n). The 'm' objects should be divided in 'n' bins by satisfying the following conditions:

- 1. Each bin can contain any number of objects.

- 2. The objects should be divided in such a way so that the successor bin should

always have more than or equal number of objects than its predecessor bin.

Example: Consider x contains y objects then (x+1) should contain  $\geq$  y objects.

Example

Consider an example of dividing 8 objects in 3 bins. The objects can be divided in the following ways:

| b1 | b2 | b3 |

|----|----|----|

| 0  | 0  | 8  |

| 0  | 1  | 7  |

| 0  | 2  | 6  |

| 0  | 3  | 5  |

| 0  | 4  | 4  |

| 1  | 1  | 6  |

| 1  | 2  | 5  |

| 1  | 3  | 4  |

| 2  | 2  | 4  |

| 2  | 3  | 3  |

In the above example if the bin 0 is filled with one object then all other should be filled with a minimum of 0 object and not less than that. Then the function for remaining objects is represented as f(8, 3) which there are 10 ways that can be filled in 3 bins.

Similarly if first bin is filled with 1 object then all other bins should be filled with a minimum of one object. The dividing process goes by following this condition till the last bin is filled with the last object.

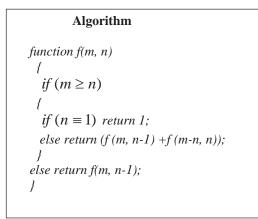

# 4. Generating an algorithm for dividing objects in non-descending order

Partitioning an integer n is to divide it into its constituent parts which are all positive integers. Algorithms for enumerating all the partitions of an integer or only the partitions with a restriction have long been invented [1,2]. Consider f(8,3) i.e dividing 8 objects into 3 bins. If bin1 contains 0 objects then the function for dividing the other objects is f(8,2) which means 8 objects should be divided in 2 bins. Similarly if bin1 contains 1 object then the function for dividing the other objects is f(5,2) which means 5 objects should be divided in 2 bins because if first bin is filled with one object then other two bins should also be filled with a minimum of one object. So the remaining objects to be filled are 8-3= 5. Similarly if bin1 and bin2 contains 2 object then the function for dividing the other objects is f(2,1) which means 1 objects should be divided in 1 bin because if first and second bean is filled with two objects then other beans should also be filled with a minimum of two objects. So the remaining objects to be filled are 8-6=2.

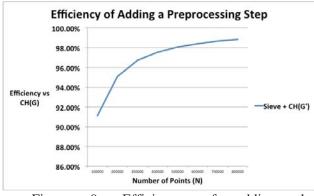

Let f(m,n) be the number of ways of dividing m objects into n bins with non-descending cardinality. Function f (m,n) for dividing m objects into n bins in this particular format is shown

$\begin{array}{l} f(m,n) = f(m, n-1) \quad // \ first \ bin \ contains \ 0 \ objects \\ + \ f(m-n, n-1) \ // \ first \ bin \ contains \ 1 \ object \\ + \ f(m-2n, n-1) \ // \ first \ bin \ contains \ 2 \ objects \\ + \ f(m-3n, n-1) \ // \ first \ bin \ contains \ 3 \ objects \\ \end{array}$

∟m/n」 objects.

#### 5. Partition Diagram

Algorithms for enumerating all the partitions of an integer or only the partitions with a restriction have been extensively studied [4], [5].

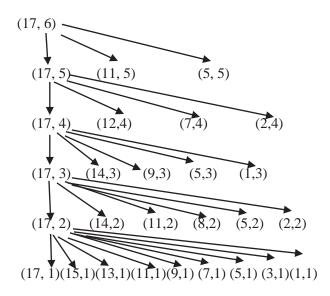

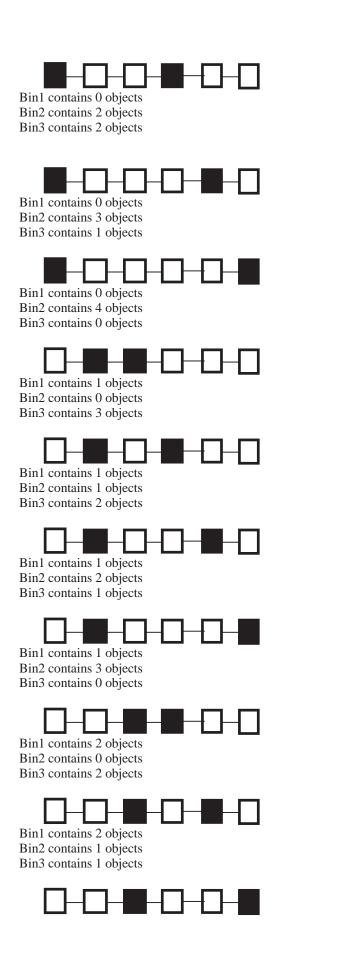

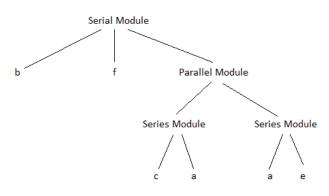

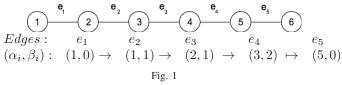

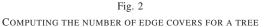

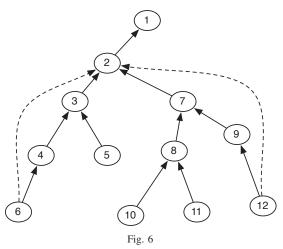

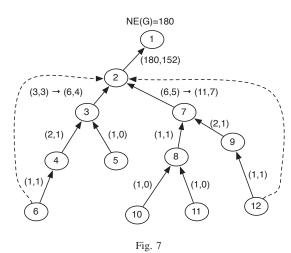

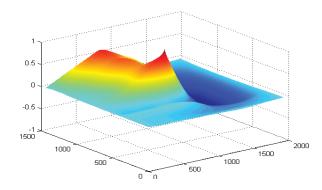

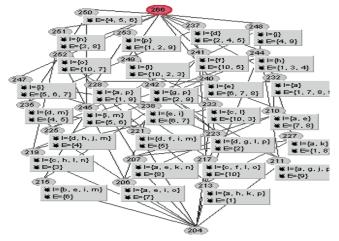

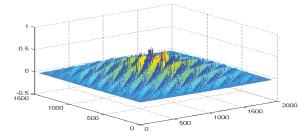

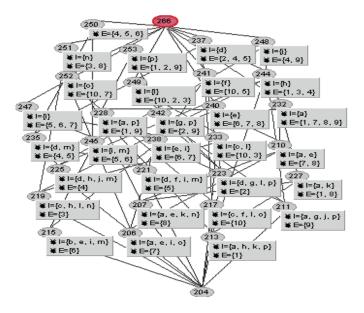

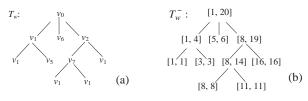

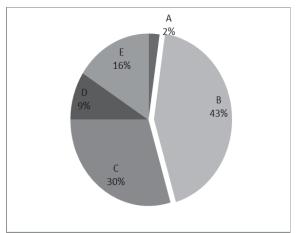

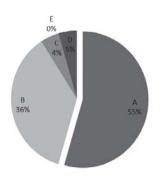

Fig.1: Patition diagram needed to divide 17 objects into 6 bins. The diagram represents a directed acyclic graph.

A data structure called partition diagram for storing all the partitions of an integer is proposed in [3]. In Merca [6], [7] improvements are proposed which, to date, are the most adequate data structures for generating integer partitions. We use the data structure proposed by Merca to present an efficient algorithm for generating ascending compositions of an integer n in m parts.

The partition diagram is a directed acyclic graph. Anode in the partition diagram is denoted by (m,n) where m is the number of objects and n denotes the number of bins. A node (m,n) that has no predecessor is called *anchored node* (*root node*) in a partition diagram. A node (m,n) which has no successor is called a *terminal node*. For example in the Fig. 1 the node (17,6) is an *anchored node* and also *internal node*, whereas node (2,1) is a *terminal node* (*leaf node*).

Given a partition diagram, a path from an anchored node to terminal node defines a unique partition in which m objects are divided into n bins.

For example in Fig. 1 the path (17, 6) (17, 5) (7, 4) (5, 3) (2, 2) defines a partition.

If the number of objects in the first bin is 'a' then all bins should have at least 'a' objects. If we allocate 'a' objects to every bin then we have (m-na) objects left to be distributed in (n-1) bins. So the process of dividing should continue till the value of m-n is greater than 0.

When we format the algorithm we can assume two situations

- *The first bin is empty* In this case *m* objects are to be distributed in (*n*-1) bins.

- The first bin contains at least one object In this case we allocate one object to every bin. Thus we have (*m*-*n*) objects left to be distributed in n bins.

Lemma 1:  $f(m,n) \le xf(m-1,n) \le nf(m-1,n)$ , where x is the number of steps explained below.

Consider m objects to be placed into n bins. Let x be the number of steps that are formed while arranging the objects.

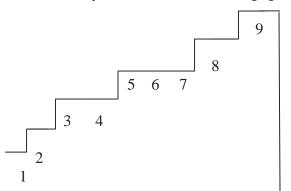

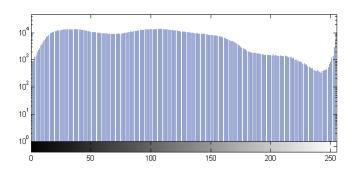

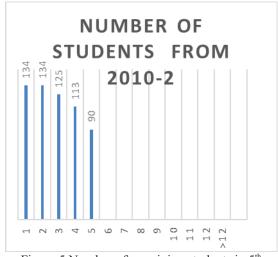

Fig. 2: Different ways of arranging the objects

If the successor bin contains more objects than the preceding bin then the objects are arranged in the form of steps in between the bins. For example in Fig. 2 shows a configuration in which bin 2 contains more number of objects than bin 1 so they are arranged as a step. Similarly bin 2 and bin 3, bin 4 and bin 5, bin 7 and bin 8, bin 8 and bin 9. If the successor bin contains the same number of objects as in the preceding bin then the arrangement is not formed as step. It remains at same level as they contain same number of objects. For example bin 3 and bin 4 contains same number of objects so they remain at same level. Similarly bin 5, bin 6 and bin 7 contain same number of objects.

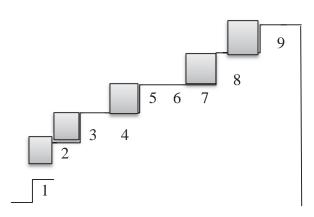

Fig.3: Different ways of adding an object in the above arrangement

If we want to add an object in the configuration shown in Fig.2, the added object should not affect the configuration i.e. the object is to be added in non-descending cardinality. As shown in Fig.3, the added object can only be placed in the shaded portion. Therefore we can say that the number of arranging the objects in the predecessor bin is always less than or equal to the number of way of arranging the objects in the form of steps. When we have a configuration for f(m-1, n) then we can generate at most xf(m-1, n) configurations when we add an object, where 'x' is the number of steps in the configuration for f(m-1, n). Hence  $f(m, n) \le xf(m-1, n)$ . Because  $x \le n$  thus  $f(m, n) \le xf(m-1, n) \le nf(m-1, n)$ .

*Lemma 2:*  $f(m,n) \le \sqrt{2m} f(m-1,n)$

From the above lemma we know that  $f(m,n) \le xf(m-1,n)$  where x is the number of steps.

Fig. 3: Arrangement of objects to achieve maximum steps

Maximum number of steps can be obtained by placing the objects in the following way. Let there be many number of objects with many number of bins. Then the objects are placed in increasing way to obtain the maximum steps in the following way

0 objects in bin 1 1 object in bin 2 2 objects in bin 3 3 objects in bin 4 . . t objects in bin t+1. Let m be the total number of objects, then m = [t (t+1)]/2By solving this we get  $t = \sqrt{2m}$ The maximum number of steps is  $\sqrt{2m}$ Therefore  $f(m, n) \le \sqrt{2m} f(m-1, n)$

Algorithms which efficiently built these kind of integer partition combinations have long been studied, a survey can be found in Knuth [8]. Although the space and time needed to store either the partition diagram or the set of kernel strings is quadratic [9], our approach creates the most efficient data structure with space and time complexity O(mn). The space and time complexity is low enough to make possible for storing all the partitions of an integer up to several ten thousands. In [3]  $O(n^2)$  storage is used for storing the partitions. Our algorithm uses less space when m is smaller than n. The implication of this result is that, in practical applications, we can efficiently recover subsets for a given path graph as kernel strings are the base to generate combined strings.

### 6. Second Approach

Consider a case in which  $x_0$  contains 0 objects,  $x_1$  contains 1 object,  $x_2$  contains 2 objects,  $x_3$  contains 3 objects..... $x_a$  contains a objects.

Let there be 'm' objects. Then we can say  $x_00+x_11+x_22+x_33+x_44...+x_aa=m$

Example: Consider an example of dividing 4 objects into 3 bins such that  $x_11+x_22+x_33=m$ The only case we have is  $x_1=1, x_2=0, x_3=1$

This method of partitioning the objects contains less number of ways than the method of partitioning objects in traditional method *i.e*  $x_0+x_1+x_2+x_3+x_4....+x_a=m$ .

Now consider the same example of dividing 4 objects into 3 bins such that  $x_1+x_2+x_3=m$

The possible cases are follows  $x_1 = 0, x_2 = 0, x_3 = 4$  $x_1 = 0, x_2 = 1, x_3 = 3$  $x_1 = 0, x_2 = 2, x_3 = 2$  $x_1 = 0, x_2 = 3, x_3 = 1$  $x_1 = 0, x_2 = 4, x_3 = 0$  $x_1 = 1, x_2 = 1, x_3 = 2$  $x_1 = 1, x_2 = 2, x_3 = 1$  $x_1 = 1, x_2 = 0, x_3 = 3$  $x_1 = 1, x_2 = 3, x_3 = 0$  $x_1 = 2, x_2 = 1, x_3 = 1$  $x_1 = 2, x_2 = 0, x_3 = 2$  $x_1 = 2, x_2 = 2, x_3 = 0$  $x_1 = 3, x_2 = 0, x_3 = 1$  $x_1 = 3, x_2 = 1, x_3 = 0$  $x_1 = 4, x_2 = 0, x_3 = 0$

# 7. Generating an algorithm for partitioning objects

Initially consider there are m+n-1 positions out of which choose n-1 positions then you will be left with m objects to be partitioned into n bins.

Example:

Consider the following 4 objects to be partitioned into 3 bins.

1. Initially consider m+n-1 positions i.e. 4+3-1=6

2. Choose n-1 positions i.e. 3-1=2. The two positions can be taken in the following ways.

Bin2 contains 0 objects Bin3 contains 3 objects

Bin1 contains 2 objects Bin2 contains 2 objects Bin3 contains 0 objects

Bin1 contains 3 objects Bin2 contains 1 objects Bin3 contains 0 objects

Bin2 contains 0 objects Bin3 contains 1 objects

Bin1 contains 4 objects Bin2 contains 0 objects Bin3 contains 0 objects

Partitioning m objects into a bins using the method  $x_00+x_11+x_22+x_33+...x_aa=m$  has definitely less number of steps than partitioning the objects in  $x_1+x_2+x_3+x_4...x_a=m$ . The space and time complexity for creating a linear structure or a partition tree is definitely less while compared to the traditional method. The ways of partitioning with  $x_00+x_11+x_22+x_33+...x_aa=m$  is always a subset of ways of partitioning objects using  $x_1+x_2+x_3+x_4...x_a=m$

Now we consider partition of '*m*' objects into bins such that a bin can contain atmost '*a*' objects. The formula for this  $is_1x_1+2x_2+3x_3+\ldots ax_a=m$  which is less than the number of ways *m* can be partitioned into *a* bins by

$$x_1 + x_2 + x_3 + \dots \dots x_a = m \text{ which is } \le \binom{m+a-1}{a-1} \tag{1}$$

Then the equation will be  $x_{a+1}(a+1)+x_{a+2}(a+2)\dots x_b b=m$

Now consider the ways *m* objects can be partitioned into bins in such a way that each bin contains at least *a* objects. The number of bins is now restricted by m/(a+1).

We first choose m/(a+1) positions among m positions with

$$\binom{m}{m/(a+1)}$$

ways (2)

and then partition m objects in non-descending as

$x_{a_1}a_1 + x_{a_2}a_2 + \dots + x_{a_{m/(a+1)}}a_{m/(a+1)} = m$

where  $a_1 < a_2 < a_3 < \dots$  Compare this case with the method of partitioning m objects into m/(a+1) bins *i.e.*

$x_1+x_2....x_{m/(a+1)}=m$

The number of ways of dividing m objects using the method

$$\binom{m + (m/(a+1)) - 1}{m/(a+1) - 1}$$

(3)

The number of ways of dividing m objects using the method

$$x_{a_1}a_1 + x_{a_2}a_2 + \dots + x_{a_{m/(a+1)}}a_{m/(a+1)} = m$$

is  $\leq (m + (m/(a+1)) - 1) / (m/(a+1) - 1))$

So the total number of ways of partitioning 'm' objects into 'm' bins is less than the product of (1), (2) and (3), that is

$$\leq \binom{m+a-1}{a-1} \cdot \binom{m}{m/(a+1)} \cdot \binom{m+(m/(a+1))-1}{m/(a+1)-1}$$

$\approx (m/a)^{a} a^{m/a} a^{m/a} \leq max[(m/a)^{3a}, a^{3m/a}]$ Therefore we let  $[m/a]^{a} = a^{m/a}$  $a \log (m/a) = (m/a) \log a$  $[a^{2}(\log m - \log a)]/\log a = m$  $a^{2} = m\log a/\log m$  $a = \sqrt{m\log a / \log m}$  $\approx \sqrt{m}$

This gives about  $m^{\sqrt{m}}$  ways, while the number of ways of partitioning objects using the formula  $x_1+x_2+x_3+x_4...x_m=m$

gives

$$\binom{m+m-1}{m-1} \approx 2^{2m}$$

### 8. Conclusion and Future work

In this paper we have studied about partitioning a set into non-descending cardinality. The space and time complexity for creating a linear structure or a partition tree is proportional to the number of partitions whereas the complexity for creating a partition diagram is only O(mn). This complexity allows us to create a partition diagram that can store all the partitions of an integer up to several ten thousands.

#### 9. Reference

- [1] D. Stanton and D. White. *Constructive Combinatorics*. Springer-Verlag, Berlin, 1986.

- [2]. C. L. Liu. *Introduction to Combinatorial Mathematics*. Mcgraw-Hill College, 1968.

- [3] R.-B. Lin, "Efficient data structure for storing the

partitions of integers," The 22nd Workshop on Combinatorics and Computation Theory, pp. 349–354, 2005.

- [4]D. Stanton and D. White, "Constructive combinatorics," SpringerVerlang, Berling, 1986.

- [5]C. L. Liu, "Introduction to combinatorial mathematics," MacGraw-Hill College, 1986.

- [6] M. Merca, "Binary diagrams for storing ascending compositions," The Computer Journal Advance Access, 2012.

- [7] ——, "Fast algorithm for generating ascending compositions," Journal of Mathematical Modelling and Algorithms, vol. 11, pp. 89–104, 2012. [Online]. Available:http://dx.doi.org/10.1007/s10852-011-9168-y

- [8] D. E. Knuth, The Art of Computer Programming, Volume 4A: Combinatorial Algorithms, Part 1. Addison Wesley, 2011.

- [9] J. Raymundo Marcial-Romero, J. A. Hernández Vianney Muñoz-Jiménez and Héctor A. Montes-Venegas Generating edge covers of path graphs. In Peoceedings of 2013 WORLDCOMP.

# Multiprocessor MMIO Tracing via Memory Protection and a Shadow Page Table

Myoungjae Kim<sup>1</sup>, Hyunmin Yoon<sup>2</sup>, Minkwan Choi<sup>1</sup>, Shakaiba Majeed<sup>1</sup>, and Minsoo Ryu<sup>1\*</sup>

<sup>1</sup>Department of Computer Science and Engineering, Hanyang University, Seoul, Korea <sup>2</sup>Department of Electronics Computer Engineering, Hanyang University, Seoul, Korea {mjkim, hmyoon, mkchoi, shakaiba}@rtcc.hanyang.ac.kr, msryu@hanyang.ac.kr

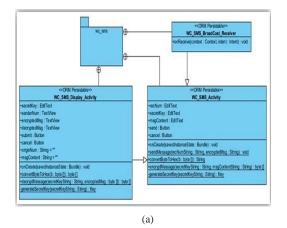

Abstract – Memory-mapped I/O (MMIO) tracing provides an effective means for analyzing and debugging I/O related functions since it allows us to observe and track the interplay between processors and I/O devices [1]. However, existing MMIO tracing techniques have a serious drawback in multicore systems. Current MMIO techniques commonly use a memory protection mechanism to detect access to an MMIO address area under consideration. Unfortunately, this approach may miss some I/O events and even lead to a data race condition due to inappropriate management of concurrent accesses to the MMIO address area. In this paper, we describe a novel MMIO tracing approach introducing the notion of shadow page table. We use a shadow page table to allow only one processor to have access to a MMIO address area while forbidding other processors' access to the same MMIO address area. We show how the shadow page table approach can be efficiently implemented on a multiprocessor platform with dual core ARM Cortex A15 CPU.

**Keywords:** Memory Mapped I/O (MMIO) Trace, Memory Protection, Page Fault, Shadow Page Table.

# **1** Introduction

Memory-mapped I/O (MMIO) tracing provides an effective means for analyzing and debugging I/O related functions since it allows us to observe and track the interplay between processors and I/O devices. For example, to analyze and debug failures in device drivers, developers must be able to find out what data is sent to or received from the device. MMIO tracing can collect detailed information about I/O operations conducted between a processor and I/O devices, thus enabling us to track down the source of failures.

However, existing MMIO tracing techniques have a serious drawback in multicore systems. Current MMIO tracing techniques commonly use a system-wide address translation table, i.e. page table in processors with paging support, to set the MMIO address area under consideration as invalid and rely on memory access exceptions to detect any processor's access to the protected MMIO address area. When an exception is generated by a read/write instruction, a specially designed exception handler collects information

about the I/O access, enables access permission for the MMIO address area, re-executes the faulting memory access instruction, and sets the access permission back to invalid. Unfortunately, in multicore hardware, this may lead to missing some I/O events and even a data race condition since other processors can make writes simultaneously to the same address area during the time interval where the access to MMIO address area is enabled.

In this paper, we present a novel MMIO tracing method introducing the notion of shadow page table. When a page fault occurs on a certain processor, we replace the page table seen by the exception handling processor with a shadow page table, while leaving other processors referencing the original page table. The shadow page allows only the exception handling processor to access the MMIO address area, but other processors' access to the MMIO area is prohibited through the original page table. Therefore, this approach allows us to avoid the problem of missing I/O events and race conditions. We describe how the shadow page table approach can be efficiently implemented on a multiprocessor platform with dual core ARM Cortex A15 CPU.

This paper is organized as follows. Section 2 describes existing MMIO tracing techniques. Section 3 presents our shadow page table approach and Section 4 concludes this paper.

# 2 Background of MMIO Tracing

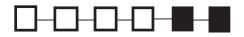

### 2.1 Memory-mapped I/O (MMIO)

MMIO requires a section of memory to allow a processor to communicate with I/O controllers. A processor with MMIO support reserves some part of its address space for a special I/O address range where I/O controllers' registers are mapped to specific addresses in the designated I/O address range. Programs can access I/O registers through memory access instructions such as load and store, which is no different from read/write access to normal memory addresses [3].

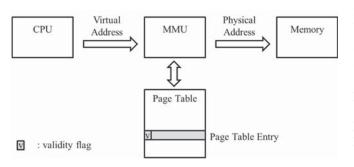

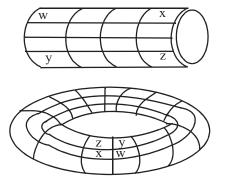

MMIO tracing can be efficiently implemented using a page table. A page table contains the mapping between virtual addresses and physical addresses and some additional information associated with each page table entry. One important piece of information is the access permission for each page. By manipulating the access permission for each MMIO page, we can allow or prohibit the processor's access to specific MMIO pages. MMIO tracing initially disables access permission for MMIO pages using the page table. Whenever a processor attempts to access a protected MMIO page, a page fault exception occurs. A special page fault handler then collects information about the I/O access, enables the access permission for the MMIO page, re-executes the faulting memory access instruction, and re-disables the access permission.

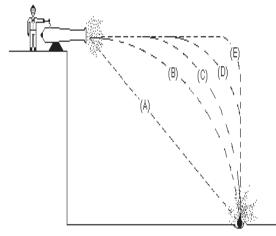

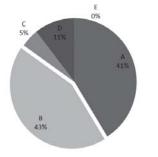

Figure 1. Address space of a Processor using MMIO.

Figure 2. Paging and translation scheme.

### 2.2 MMIO Tracing in Linux

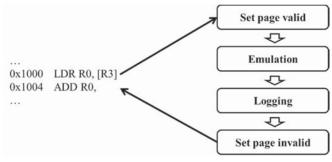

The Linux MMIO tracing tool uses a validity attribute associated with each page table entry to force page fault to occur when a processor accesses a memory mapped I/O region even if the region exists in a valid page [5]. The tool records the MMIO accesses in the following way: First, the MMIO pages are marked as invalid. When a fault occurs due to an access to these pages, the page fault handler emulates the faulting instruction by changing the attribute of the page as valid and starts logging the events. After the emulation and logging the page fault handler again marks the page as invalid. Finally, the interrupted kernel code takes control again and executes the next instruction to the faulting instruction.

While the page fault handler is emulating the faulting instruction, the other processors can freely access the page containing the data which the faulting instruction wanted to access because that page is marked valid during this interval. In such situation, other processor's access does not create a page fault which leads to event missing without notice.

Figure 3. Tracing control flow.

# 3 MMIO Tracing with a Shadow Page Table

As mentioned earlier, existing MMIO tracing techniques based on a memory protection mechanism may fail to capture some concurrent I/O events on multiprocessors. The problem is that other processors can make references to the same MMIO address area during the interval the memory access is allowed. Those accesses cannot be detected as they do not trigger page fault exceptions and may even lead to data race conditions.

A plausible solution is freezing other processors during the page fault handling. When a page fault happens, we may stop other processors' execution by sending a special interprocessor interrupt (IPI) to other processors. This would prevent other processors from accessing the MMIO address area. However, sending and receiving IPIs also requires access to the interrupt controller's MMIO addresses, which would entail the same problem.

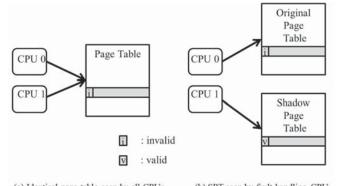

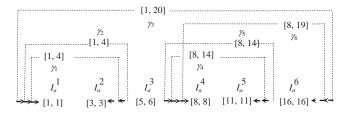

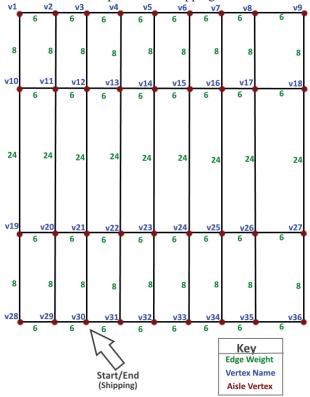

(a) Identical page table seen by all CPUs (b) SPT seen by fault-handling CPU

Figure 4. Shadow Page Table.

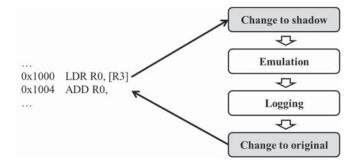

In order to address the above problem, we propose the use of a shadow page table (SPT). When a page fault occurs, a shadow page table replaces the kernel's original page table used by the fault handling processor. The use of shadow page table allows us to enable the access permission of the fault handling processor while other processors' memory access is prohibited by the original kernel's page table. Therefore, this approach can overcome the problem of missing I/O events and race conditions.

The shadow page table can be efficiently implemented in many operating systems that support paging-based memory management. We replicate the original kernel's page table and modify the access rights to the MMIO address areas in the replicated shadow page table to enable access permission. When a page fault occurs, we change the page table base register of the processor so that it can refer to the shadow page table during the page fault handling. Since other processors still refer to the original page table, they are not allowed to make access to the MMIO address areas. Once logging MMIO I/O access information is done, we change the page table base register to point to the original page table. Afterwards, all the processors use the original page table. There is a possibility that two more processors try to write access on a same MMIO address almost at the same time. It also leads to data race condition as two processors re-execute the faulting memory access instructions. To prevent this problem, we need to protect fault handling as a critical section with a synchronization method such as spin lock.

Figure 5. Tracing control flow with SPT.

## 4 Conclusion

In this paper, we have presented a novel MMIO tracing method introducing the notion of shadow page table. Letting a processor refer to shadow page table while it conducts MMIO tracing, we can solve a problem of missing another MMIO event by other processors as well as data race condition under multiprocessor platform.

## **5** Acknowledgment

This work was supported partly by Seoul Creative Human Development Program (HM120006), and partly by the National Research Foundation of Korea(NRF) grant funded by the Korea government(MEST) (NRF-2011-0015997), and partly the MSIP(Ministry of Science, ICT and Future Planning), Korea, under the C-ITRC(Convergence Information Technology Research Center) (IITP-2015-H8601-15-1005) supervised by the IITP(Institute for Information & communications Technology Promotion).

## **6** References

[1] Wikipedia, "Memory-mapped I/O," [Online]. Available: http://en.wikipedia.org/wiki/Memory-mapped\_I/O

[2] A. Kadav and M. M. Swift, "Understanding modern device drivers," *ACM SIGARCH Computer Architecture News*, vol. 40, pp. 87-98, 2012.

[3] D. P. Bovet and M. Cesati, *Understanding the Linux kernel*: "O'Reilly Media, Inc.", 2005

[4] Wikipedia, "Virtual memory," [Online]. Available: http://en.wikipedia.org/wiki/Virtual\_memory

[5] LWN, "Tracing memory-mapped I/O operations," [Online]. Available: https://lwn.net/Articles/270939/

# **SESSION**

# GRAPH AND NETWORK BASED ALGORITHMS + FORMAL METHODS AND APPLICATIONS + QUANTUM COMPUTING AND RELATED ISSUES

Chair(s)

TBA

# Beyond the Solution to 2-CSC: $O(n^2)$ Algorithm to Discover Corresponding Chain Subgraph Covers

Wei-Da Hao<sup>1</sup> and Lin-Yu Tseng<sup>2</sup>

<sup>1</sup> Electrical Engineering and Computer Science, Texas A&M University – Kingsville, Kingsville, TX 78363, USA <sup>2</sup> Computer Science and Communication Engineering, Providence University, Taichung 43301, ROC

**Abstract**— The algorithm proposed in this paper accepts as input an arbitrary bipartite G and responds with corresponding chain sub-graph covers, if G is recognized as coverable by two or less chain sub-graphs and responds "no" otherwise. The component ideas of a solution to the 2-CSC problem by Tze-Heng Ma and Jeremy Spinrad in 1994 are compiled into applicable steps and assembled to construct the proposed algorithm. The time complexity is  $O(n^2)$ , where n is the number of vertices of G. Related problems that can find this research useful are discussed in the conclusion.

Keywords—2-CSC; chain; sub-graph; bipartite; recognition

# 1. Introduction

In this paper, we design an effective algorithm, which has time complexity  $O(n^2)$ , for obtaining more informative outcome from a previous solution to 2-chain subgraph cover (2-CSC) problem [1]. The input to the 2-CSC problem is any bipartite graph G, and the expected output is a "yes" or "no" answer that responds to the question if G can be covered by two or one chain sub-graph.

In many occasions, a "yes" output generated from the 2-CSC problem is not informative enough, and we usually want to know the corresponding chain sub-graph covers as well. While most of the supporting properties and theorems enabling the discovering of the desired chain sub-graph covers are implied in the solution to the 2-CSC problem, an applicable algorithm has yet been designed.

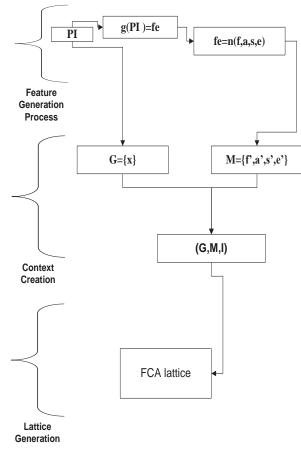

Thus, we look into the solution to the 2-CSC problem in detail. Inspect supporting theorems and properties to each step for useful information to develop the algorithm discovering chain sub-graph covers. At the beginning of the solution to 2-CSC problem, a partial order P is derived from the input bipartite graph G. Then, the algorithm examining if the dimension of a partial order is two is applied to P. Since, by theorem, the dimension of P derived from G is the same as the minimum number of chain sub-graph covering of G [1], we can get the "yes" or "no" answer to a 2-CSC problem from the outcome of previous algorithm. This paper intends to go beyond a "yes" answer and substantializes the useful information implied in the above computing process for the algorithmic steps to discover the corresponding chain sub-graph covers.

## **2. Definitions**

#### 1. Graph

Graph *G* is composed of set of vertices *V* and set of edges *E*, expressed in G = (V, E). Assume  $u, v \in V$ . For directed graph, edge  $(u, v) \in E$  represents the connection from *u* to *v*, which is a directed edge. For undirected graph, edge  $uv \in E$  or  $vu \in E$  represents the connection between *u* and *v*, which is an undirected edge.

#### 2. Bipartite graph

Let G = (V, E) represent a bipartite graph. What's different from general graph is that *V* can be partitioned to two sets *X* and *Y*, and edge only exists between *X* and *Y*. To distinguish from general graph, we use B = (X, Y, E) to represent a bipartite graph, and every edge  $uv \in E$  (for directed graph,  $(u, v) \in E$ ), either  $u \in X$  and  $v \in Y$ , or  $v \in X$  and  $u \in Y$ .

#### 3. Chain graph

Chain graph is an undirected bipartite graph that its edge set doesn't contain  $2K_2$ , which is two undirected edges uv and wx, that either  $uw \notin E$  and  $vx \notin E$ , or  $ux \notin E$  and  $vw \notin E$ .

#### 4. K-CSC and 2-CSC problem

K-CSC is abbreviation of "K-Chain Sub-graph Cover". K-CSC problem is a problem about the question if an input bipartite graph can be covered by K chain sub-graphs. It has been proved that when  $K \ge 3$ , K-CSC problem is NP-complete. When K = 2, K-CSC problem is a 2-CSC problem.

#### 5. ch(G)

ch(G) is the smallest number K such that bipartite graph G is K-chain sub-graph coverable.

#### 6. Partial order [2]

Partial order P defines the dominant relationship R between some pairs of elements in a group of elements X, expressed by P = (X, R). R is transitive and non-reflexive binary relationship on X. For  $x, y \in X$ ,  $(x, y) \in R$  indicates x dominates y, expressed by x < y. If either x < y or x > y, x and y are comparable. If neither x < y nor x > y, x and y are non-comparable. For  $x, y, z \in X$ , if  $(x, y) \in R$  and  $(y, z) \in$ R, it can be concluded, through the fact that R is transitive, that x < z, but  $(x, z) \in R$  may not be true.

#### 7. Extension of a partial order

For a partial order P = (X, R), its extension is another partial order P' = (X, R'), such that  $R \subseteq R'$ . If every pair of elements of X is comparable in P', P' is a linear extension of P.

#### 8. *Linear order(total order)*

If a partial order has no incomparable pair, it is called a linear order.

#### 9. Dimension of Partial Order

Dushnik and Miller defined the dimension of a partial order P [2], dim(P), as "the minimum number of total orders whose intersection defines the partial order".

#### 10. 2-Dimensional partial order problem

This is a problem to determine if a given partial order whose dimension is two or less than two.

# 11. Modular Decomposition of a DAG (Directed Acyclic Graph)

DAG G = (V, E) is used to represent a partial order P = (V, R), such that for  $x, y \in V$ :  $(x, y) \in E$  if and only if  $(x, y) \in R$ . x, y are related in DAG G, if  $(x, y) \in E$  or  $(y, x) \in E$ . Otherwise, x, y are not related in DAG G. Since R is transitive, DAG G is a transitive graph.

1) Representation of a DAG: The linear orders on V whose intersection is P construct the representation of the DAG G.

2) Listing and Non-separating listing: Each linear order of the representation for a DAG *G* is called a listing. Between two comparable elements u, v of P in a listing, if there is no element that is not comparable to both u and v, the listing is a non-separating listing.

3) Two dimensional partial order of a DAG G = (V, E): Each linear order of the representation for a DAG G is called a listing. Between two comparable elements u, v of P in a listing, if there is no element that is not comparable to both u and v, the listing is a non-separating listing.

4) Module *M*: Module *M* is a subset of *V* with the property that for  $v \in V - M$ , either *v* is related to every vertex in *V* or not at all.

5)  $M_C: M_C$  is the undirected graph that has M as vertex set, and for  $u, v \in M$ , uv is an edge in  $M_C$ , if u, v are related in DAG G.

6)  $M_{CC}$ :  $M_{CC}$ , of is the undirected graph that has M as vertex set, and for  $u, v \in M$ , uv is an edge in  $M_{CC}$ , if u, v are not related in DAG G.  $M_C$  and  $M_{CC}$  are complementary to each other.

7) Maximal submodule: A module M is said to be a maximal submodule of another module N, if  $M \subset N$  and no proper submodule of N contains M.

8) Parallel module: If  $M_c$  is not connected, M is a parallel module. The vertices of a parallel module can be partitioned into two subsets, so that none of the vertex in one subset is related to any vertex of the other.

9) Series module: If  $M_{CC}$  is not connected, M is a series module. The vertices of a series module can be partitioned into two subsets, so that any of the vertexes in one subset is related to any vertex of the other.

10) Neighborhood module: If both  $M_C$  and  $M_{CC}$  are connected, M is a neighborhood module.

# **3.** Properties, algorithms and theorems

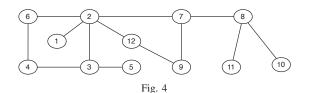

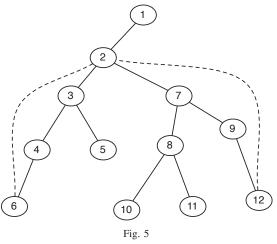

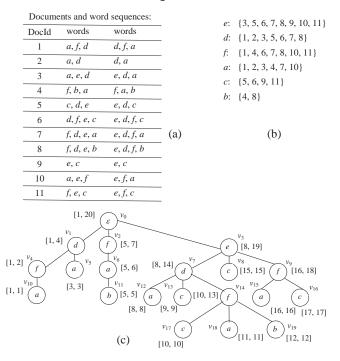

Given a bipartite graph G = (X, Y, E),  $X = \{x_1, x_2, \dots, x_l\}$ ,  $Y = \{y_1, y_2, \dots, y_m\}$ , a partial order  $P = (X \cup Y, R)$  can be generated from *G* through the following steps [1] in sequence:

Algorithm 1 Convert Bipartite Graph to Partial Order INPUT:

$$G = (X, Y, E), X = \{x_1, x_2, \dots, x_l\}, Y = \{y_1, y_2, \dots, y_m\}$$

OUTPUT:

A partial order  $P = (X \cup Y, R)$

BEGIN

- 1. Compute neighborhood of v, N(v), where  $v \in X \cup Y$ .

- 2. For those vertices having the same neighborhood, keep only one for the rest of steps.

- 3. If  $N(x_i) \supset N(x_i)$ , add  $(x_i, x_i) \in R$ .

- 4. If  $N(y_i) \supset N(y_i)$ , add  $(y_i, y_i) \in R$ .

- 5. If  $x_i y_i \notin E$ , add  $(y_i, x_i)$  to *R*.

- 6. For  $v \in X \cup Y$ , let  $U_X(v) = \{u | u \in X \text{ and } (v, u) \in R\}$ . If  $U_X(y_j) \subseteq U_X(x_i)$ , add  $(x_i, y_j) \in R$ .

END

And, an undirected bipartite graph  $B(P) = (X \cup Y, X' \cup Y', E_{B(P)})$ , where  $X' = \{x' | x \in X\}$  and  $Y' = \{y' | y \in Y\}$ , can be generated from  $P = (X \cup Y, R)$  above through the following steps [1]:

Algorithm 2 Generate B(P) from PINPUT:  $P = (X \cup Y, R)$ OUTPUT:  $B(P) = (X \cup Y, X' \cup Y', E_{B(P)})$ BEGIN 1. For  $a, b \in X \cup Y$  and  $a \neq b$ , if a < b in P, let  $ab' \in E_{B(P)}$ .

2. For  $a, b \in X \cup Y$  and  $a \neq b$ , if  $a \sim b$  in P, let  $ab' \in E_{B(P)}$ . END

Lemma 1 [1]  $ch(G) = \dim(P) = ch(B(P))$

Lemma 2 [1]

There is one-to-one mapping between the linear order of P and maximal chain sub-graph of B(P).

By lemma 1, if dim(*P*) = 2, ch(G) = 2. By lemma 2, a maximal chain sub-graph of  $B(P) = (X \cup Y, X' \cup Y', E_{B(P)})$  can be obtained from a linear order of *P*. We realize this fact by looking into the supporting logic to lemma 2 and design the following steps to compute the desired maximal chain sub-graph.

Algorithm 3 Map Linear Order to Maximal Bipartite Graph BEGIN

- 1. Given a linear order L on  $X \cup Y$  of  $P = (X \cup Y, R)$

- 2. Define the corresponding maximal bipartite graph  $H = (X \cup Y, X' \cup Y', E)$ , where  $ab' \in E$ , if a < b in L.

END

#### Lemma 3 [1]

G = (X, Y, E) is a sub-graph of  $B(P) = (X \cup Y, X' \cup Y', E_{B(P)})$  induced by X and X'.

#### Lemma 4

There is one-to-one mapping between the maximal chain subgraph of G and the maximal chain sub-graph of B(P).

#### Proof: